ساختار ارجاع انتخابی;

در قسمت ششم از آموزش FPGA با ساختار ارجاع شرطی آشنا شدیم، سپس یک ALU را با استفاده از این ساختار توصیف، و در نهایت برای صحت عملکرد ALU موردنظر، یک فایل Test Bench ساختیم و در نرمافزار ALU ،ISIM را شبیهسازی کردیم.

در این قسمت قصد داریم با ساختار ارجاع انتخابی آشنا شویم و یک مدار دیجیتال را با استفاده از این ساختار پیاده سازی کنیم. و درنهایت به مقایسه ساختار ارجاع شرطی و انتخابی بپردازیم و کاربردهای هر کدام را بیان کنیم.

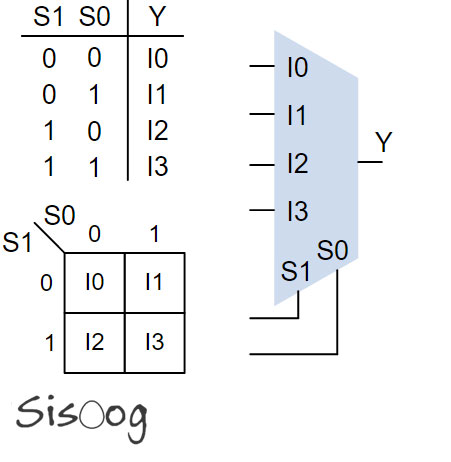

مداری که قرار است با استفاده از ساختار ارجاع انتخابی توصیف کنیم، یک مالتی پلکسر 4 به 1 خواهد بود. پس بهتر است قبل از نوشتن کد مربوطه، نگاهی کوتاه بر ساختار مالتیپلکسر و روش کار آن داشته باشیم.

مالتیپلکسر مداری میباشد که با استفاده از خط فرمان یا انتخاب، یکی از چندین سیگنال ورودیاش را انتخاب میکند و سپس آن ورودی انتخاب شده را به یک خط خروجی انتقال میدهد. برای فهم بیشتر موضوع میتوانید شماتیک و جدول صحت زیر را مشاهده کنید تا مفهوم مالتیپلکسر را به خوبی فرا گیرید.

در این ساختار، ما یک سیگنال را به عنوان سیگنال شرط، انتخاب میکنیم و با توجه به مقدار این سیگنال یک سری عملیات انجام خواهد شد.

در ادامه کدی خواهیم نوشت که شما با توجه به این کد، میتوانید با ساختار ارجاع انتخابی آشنا شوید. همچنین پس از نوشتن کد، نکاتی را در مورد این ساختار بیان خواهیم کرد.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 |

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; entity MUX is Port ( I0 : in STD_LOGIC; I1 : in STD_LOGIC; I2 : in STD_LOGIC; I3 : in STD_LOGIC; S : in unsigned (1 downto 0); Y : out STD_LOGIC ); end MUX; architecture Behavioral of MUX is begin with S select Y <= I0 when "00", I1 when "01", I2 when "10", I3 when others; end Behavioral; |

در کد بالا، چهار ورودی تک بیتی، از نوع std_logic برای ورودیهای مالتیپلکسر و همچنین یک ورودی 2 بیتی نیز از نوع unsigned برای پوشش دادن چهار حالت ورودی مالتیپلکسر در نظر گرفتیم. در نهایت یک خروجی تک بیتی از نوع std_logic برای اینکه یکی از چهار ورودی انتخاب شده به خروجی منتقل شود نیز در نظر گرفتیم.

پس از اینکه پورتهای ورودی-خروجی را انتخاب کردیم، نوبت به توصیف مالتیپلکسر با استفاده از همین پورتها میرسد. اگر دقت کنید سیگنالی که قرار است به عنوان سیگنال شرط عمل کند بین دو کلمه کلیدی with و select قرار میگیرد. در خطوط بعد، همان ورودی که قرار است با شرط خاصی، به خروجی منتقل شود را مینویسیم و به خروجی ارجاع میدهیم. پس از آن با استفاده از کلمه کلیدی when، مقدار شرط مورد نظر را مینویسیم. به همین ترتیب تا آخر برای بقیهی ورودیها نیز شرطهای موردنظر را مینویسیم.

ولی نکتهای در این ساختار وجود دارد که بهتر است به آن توجه کنید. اما قبل از پرداختن به این نکته، باید با موضوعی دیگر آشنا شویم. پس با دقت به توضیحات زیر توجه کنید.

هر سیگنال std_logic میتواند 9 مقدار مختلف داشته باشد. از این 9 مقدار، فقط مقادیر 0 و 1 و Z قابل پیادهسازی هستند و در نهایت میتوانند سنتز شوند.

وقتی سیگنالی همانند سیگنال S در کد بالا، 2 بیتی باشد، در مجموع میتواند 81 حالت مختلف داشته باشد. اما همانطور که گفتیم همهی این حالتها در پیادهسازی استفاده نمیشوند.

در کد بالا ما روی سیگنال شرط (S)، سه حالت مختلف را تعریف کردیم. برای توصیف مالتیپلکسر یک حالت دیگر، یعنی حالت “11” باقی میماند. برای این حالت از when استفاده نکردیم، بلکه از when others استفاده شده است. با توجه به توضیحات بالا، when others به 78 حالت باقیمانده اشاره میکند که یکی از این حالات، حالت “11” میباشد.

تا الان با دو ساختار در محیط Concurrent آشنا شدیم، یعنی ساختار ارجاع شرطی و ساختار ارجاع انتخابی. اما این دو ساختار تفاوتهایی نیز با هم دارند که در زیر به این تفاوتها خواهیم پرداخت.

تا اینجا هرآنچه که نیاز بود در مورد مدارات ترکیبی و محیط Concurrent بدانید بیان گردید. شما میتوانید با استفاده از توضیحاتی که ما در مورد محیط Concurrent و همچنین انواع ساختارها در این محیط بیان کردیم، هر مدار ترکیبی که مدنظرتان باشد را خلق کنید.

در قسمت هشتم با مدارات ترتیبی و محیط Sequential آشنا خواهیم شد. پس با سیسوگ همراه باشید.

مطالبتون بسیار عالی بود و حتی از استاد هم کامل تر گفتین خیلی ممنون

سپاس از شما مریم نازنین. حقیقتش در حق بنده کمی اغراق فرمودید، من در بهترین حالت شاید فقط بتونم بخشی از علم فنی استاد را انتقال بدم. اینکه استاد ثقفی در کنار علم فنی به ما علم اخلاق هم یاد دادن رو فقط باید از خود ایشون فرا گرفت و فقط خود استاد میتونن انتقالش بدن.

سپاس از لطفی که به من دارید. موفق باشید.

سیسوگ با افتخار فضایی برای اشتراک گذاری دانش شماست. برای ما مقاله بنویسید.