در این مقاله مفاهیم کلی مرتبط با منابع ورودی و خروجی FPGA مرور میشود. سپس به شکل مختصر مهمترین ویژگیهای این منابع معرفی میشوند. این مقاله به طور خاص برای تراشههای سری ۷ شرکت Xilinx نوشته شده است، اما بسیاری از تعاریف ارائه شده برای سایر خانوادهها قابل تعمیم است.

شاید برای شما مفید باشد: آموزش FPGA

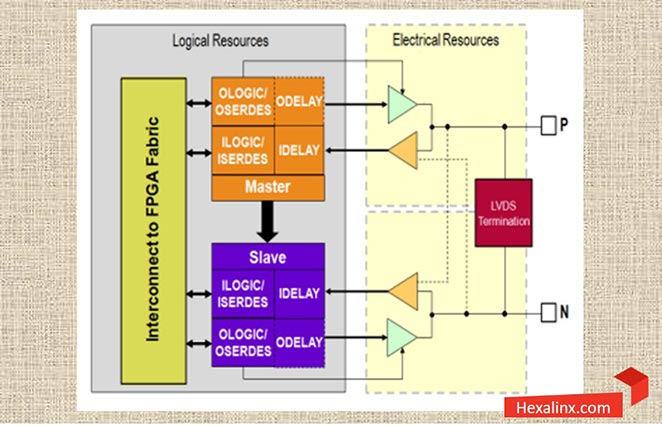

به طور کلی منابع ورودی/خروجی در هر FPGA، منابعی هستند که بین پینها و منابع منطقی درون تراشه قرار گرفته اند. این منابع به لحاظ ساختاری از دو بخش تشکیل شدهاند:

معماری داخلی یک بلوک ورودی/خروجی در تراشههای سری ۷ (Input/Output Block – IOB)

اگر با FPGA آشنایی ندارید اول مقاله FPGA چیست؟ را مطالعه نمایید.

دسته بندی منابع ورودی و خروجی FPGA در قالب بانکهای ورودی/خروجی انجام میشود. تعداد این بانکها کاملا به نوع تراشه و پکیج آن وابسته است. در حالت کلی ویژگیهای الکتریکی هر ورودی یا خروجی با توجه به قیود قابل تعریف برای هر بانک، تعیین میشود. البته موارد استثنا نیز وجود دارد که باید به آنها توجه کرد.

با توجه به متفاوت بودن تعداد بانکها بسادگی میتوان حدس زد که تعداد پینهای ورودی/خروجی نیز با توجه به نوع پکیج و منابع درون تراشه متفاوت است. بلوکهای ورودی/خروجی با استفاده از ابزارهای گرافیگی Xilinx به سادگی قابل پیکرهبندی هستند و با بسیاری از استانداردهای الکتریکی سازگار هستند. توجه شود که تمامی پینهای فیزیکی روی تراشه به صورت IO قابل استفاده نیستد. با این وجود تعداد قابل توجهی از آنها به عنوان ورودی/خروجیهای همه منظوره در دسترس هستند. در هر پکیج بجز تعداد محدودی از پینها که به تامین تغدیه مورد نیاز تراشه و پیکرهبندی آن اختصاص دارند. سایر پایهها تقریباً مشابه هم هستند و قابلیتهای یکسانی دارند.

بانکهای ورودی/خروجی در تراشههای سری ۷ در دو کلاس HR و HP دسته بندی میشوند.

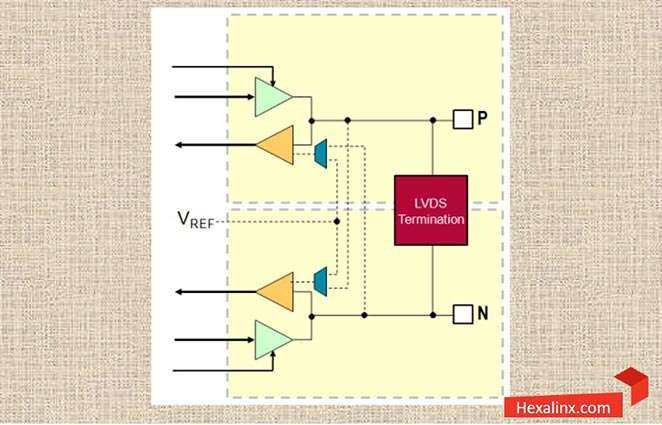

هر کدام از بانکها در تراشههای FPGA دارای ۵۰ پین ورودی/خروجی هستند. این پینها در اصطلاح SelectIO نام گذاری شدهاند. از این ۵۰ پین ۲ پین به صورت انحصاری تنها با استاندارهای سیگنالهای تک سیم سازگار هستند و ۴۸ پین باقی مانده به صورت ۲۴ زوج تفاضلی یا ۴۸ پین تکی قابل پیکرهبندی هستند. این ۴۸ پین به صوت دو به دو با برچسبهای P و N نام گذاری میشوند.

معماری بخش الکتریکی یک بلوک ورودی/خروجی

از نظر الکتریکی هر کدام از SelectIO ها میتوانند خواص متفاوتی داشته باشند. رفتار آنها به عنوان یک درایور خروجی و یا گیرنده ورودی با توجه به خواص الکتریکی که به آن بانک نسبت داده میشود، تعیین میشود. هر SelectIO دارای سه نوع درایور ورودی، خروجی و سه حالته است.

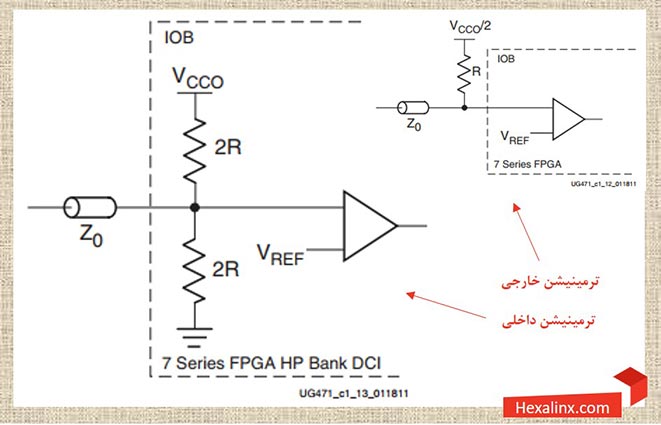

قبل از اتمام بحث در این بخش بد نیست کمی در مورد DCI صحبت کنیم. البته باید یادآور شویم، نکاتی که در ادامه بیان میشود صرفا یک معرفی کوتاه است. خاتمه دادن یک خط انتقال با استفاده از یک مقاومت برای مدل کردن خصوصیات مصرف کننده در انتهای خط اصطلاحا تِرمینیشن (Termination) نامیده میشود. به بیان دقیقتر ترمینیشن روشی برای کاهش یا از بین بردن انعکاسهای ناخواسته در یک خط انتقال است. این انعکاسها باعث ایجاد اثرات ناخواسته و نویز در سیستم میشود. از نقطه نظر سختافزاری استفاده از تِرمینیشن مناسب یک ملاحظه مهم در طراحی محسوب میشود.

با بزرگتر شدن تراشههای FPGA و بالاتر رفتن سرعت کلاک سیستم، ساخت بوردهای مدار چاپی روز به روز سخت تر میشود. طراحان سخت افزار میدانند که کنترل یکپارچگی سیگنال در زمان انتشار یا همان Signal Integrity بخش مهمی است و حتما باید مورد توجه قرار بگیرد. مفهوم امپدانس قابل کنترل دیجیتال یا DCI دقیقا برای پاسخ گویی به چنین نیازی طراحی شده است.

جایگزینی ترمینیشن خارجی با ترمینیشن داخلی با استفاده از DCI

تقریبا تمامی استانداردهای تفاضلی توسط ورودی/خروجیها پشتیبانی میشود، از LVDS تا HSTL همگی قابل تنظیم هستند.

برای مطالعه ادامه این مطلب به لینک منبع مراجعه بفرمایید.

من میتوانم ۷۰ کلمه را در دقیقهای بنویسم و حتی خودم از خواندنش عاجز باشم. بیشتر اوقاتم را با کامپیتورم میگذرانم تا با خانوادهام. بله من یک مهندس طراح الکترونیک هستم.

مقالات بیشتر

نویسنده شو !

سیسوگ با افتخار فضایی برای اشتراک گذاری دانش شماست. برای ما مقاله بنویسید.