در بسیاری از الگوریتمهای پردازش سیگنالهای دیجیتال، نیاز به انجام محاسباتی، روی اعداد مختلط دارید. اما در FPGAها (و به طور کلی در تمامی مدارات دیجیتال)، تحقق فیزیکی یا مداری خاص برای پیادهسازی اعداد مختلط وجود ندارد؛ بنابراین، جهت پیادهسازی و انجام محاسبات روی این اعداد، میبایست از روش خاصی استفاده کرد.

شاید برای شما مفید باشد: آموزش FPGA

در زبان VHDL، تایپ یا نوع دادهای برای تعریف یک سیگنال، به صورت مختلط نداریم. در عین حال، در بسیاری از الگوریتمهای پردازش سیگنال، شما نیاز دارید محاسبات مختلفی مانند ضرب و جمع را، روی اعداد مختلط انجام دهید. بنابراین، سوالی که پیش میآید این است که چگونه این کار را در مدارات دیجیتال انجام دهیم؟

در این آموزش، قصد دارم به صورت کوتاه و کاربردی، با ذکر یک مثال و به کمک کد VHDL، اعداد مختلط را در FPGA پیادهسازی کنم.

همانطور که میدانیم، هر عدد مختلط شامل دو بخش حقیقی (Real) و موهومی (Imaginary) است. به عنوان مثال، عدد مختلط X، به صورت زیر نمایش داده میشود:

X = xr + j xi

که در آن، xr، بخش حقیقی و xi، بخش موهومی X است.

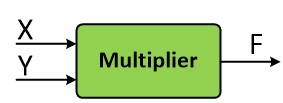

اکنون فرض کنید که میخواهیم ضرب دو عدد مختلط X و Y را در FPGA پیادهسازی کنیم. پس، همانند شکل زیر، دو ورودی X و Y، و یک خروجی F خواهیم داشت:

اما برای اینکه پورتهای مختلط ورودی و خروجی را در FPGA نشان دهیم چه راهحلی داریم؟

اگر با FPGA آشنایی ندارید اول مقاله FPGA چیست؟ را مطالعه نمایید.

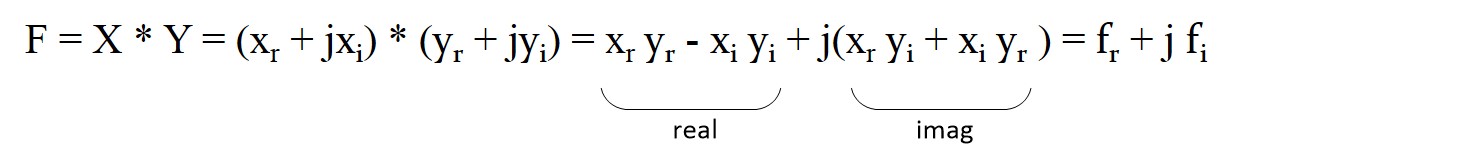

ابتدا اجازه دهید، ضرب این دو عدد را روی کاغذ انجام دهیم و آن را ساده کنیم؛ برای حاصلضرب X و Y رابطهی زیر را خواهیم داشت:

پس، خروجی F، از یک بخش حقیقی Fr و یک بخش موهومی Fi تشکیل شده است.

بنابراین، با محاسبهی سادهای که روی کاغذ انجام دادیم، تکلیف ما برای پیادهسازی مشخص شد؛ بدین ترتیب که با داشتن بخشهای حقیقی (fr) و موهومی (fi) از سیگنال F، حاصلضرب X و Y را خواهیم داشت. حالا کافی است تا دو عبارت fr و fi را در FPGA و به کمک کد VHDL پیادهسازی کنیم.

روشی که برای نشان دادن ورودی و خروجیهای مختلط در FPGA، استفاده میکنیم این است که به ازای هر عدد مختلط، دو سیگنال تعریف میکنیم؛ یک سیگنال را برای بخش حقیقی، و دیگری را برای بخش موهومی عدد مختلط در نظر میگیریم. درواقع، ورودی و خروجیهای سیستم ما به شکل زیر خواهند بود:

نویسنده شو !

سیسوگ با افتخار فضایی برای اشتراک گذاری دانش شماست. برای ما مقاله بنویسید.