تاریخچه و قابلیتهای خاص پروتکل JTAG

اگر با میکروکنترلرها زیاد سر و کار دارید و آنها را پروگرام کرده باشید به احتمال زیاد اسم JTAG را نیز زیاد شنیدهاید، اما چرا؟ چون از JTAG غالبا برای پروگرام و دیباگ تراشههای زیادی از جمله میکروکنترلرها استفاده میشود و افرادی که درگیر پروگرام تراشههای مختلف هستند حتما اسم این پروتکل را شنیدهاند. اما JTAG چیست؟

شاید برای شما مفید باشد: آموزش FPGA

تاریخچه

در دهه 1980 میلادی به دنبال راه حلی برای استانداردسازی بردهای چند لایه بودند تا اینکه در نهایت استانداردی مرتبط با این موضوع تحت عنوان JTAG ارائه شد. اما این پروتکل گستردهتر شد و به سمت کاربردهای دیگری رفت که ما در ادامه به این کاربردها اشاره خواهیم کرد.

دیباگ

اگرچه JTAG برای اولین بار به منظورهای دیگری در رابطه با تستهای سطح برد استفاده میشد اما اکنون JTAG برای دیباگ کردن دستگاهها، آزمایش سیستمها و تشخیص خطاها طراحی شده است. امروزه JTAG به عنوان اصلیترین وسیله برای دسترسی به بلوکهای مدارات مجتمع مورد استفاده قرار میگیرد و به یک مکانیزم اساسی برای دیباگ سیستمهای امبدد (embedded) تبدیل شده است که ممکن است دیگر کانال ارتباطی با قابلیت دیباگ نداشته باشند.

در اغلب سیستمها، دیباگ مبتنی بر JTAG از اولین کلاک پس از ریست CPU در دسترس است، که این اجازه را میدهد boot اولیه قبل از راهاندازی هر چیزی اجرا شود.

یک شبیهساز درون مدار، از JTAG به عنوان مکانیزمی برای دسترسی به بلوکهای اشکالزدایی داخلی استفاده میکند و این مورد این اجازه را به توسعهدهندگان نرمافزار میدهد تا نرمافزار یا همان کد امبدد سیستم را در سطح کد ماشین یا سطوح بالاتر دیباگ کنند.

قابلیتهای زیاد و کاربردهای فراوانی که JTAG دارد، از جمله ردیابی دستورالعملها و همچنین دسترسی به تمامی رجیسترها و حافظهها مانند RAM و FLASH این پروتکل را منحصر به فرد کرده است.

به عنوان مثال میتوان به دو شیوه روند تست ایجاد کنید. اما این دو شیوه و روش به چه نحوی عمل میکنند؟

ما میتوانیم برنامه خود را پروگرام کنیم و زمانی که برنامه در حال اجراست حافظهها یا سیگنالهای بخشهای مختلف مدار را در نرمافزاری که با استفاده از پروتکل JTAG با مدار در ارتباط است مانیتور کنیم. روش دیگر این است که ما با استفاده از همین پروتکل JTAG وقتی برنامه در حال اجرا است، مقادیر حافظههای داخلی را میتوانیم تغییر بدهیم و سپس نتیجه تغییرات حاصله را مانیتور کنیم.

این موضوع در FPGAها نیز وجود دارد و شما میتوانید با استفاده از نرمافزار chipscope و ipcoreهایی که وجود داد هر دو روند تست بالا را انجام دهید، فقط توجه کنید که در روند تست دوم قرار نیست کد جدیدی درون FPGA سنتز شود بلکه کد سنتز شده همان است و فقط مقادیر بعضی از منابع یا حافظهها تغییر خواهد کرد. (برای درک این موضوع نیاز است که با مفاهیم و چگونگی برنامهریزی FPGAها آشنا باشید)

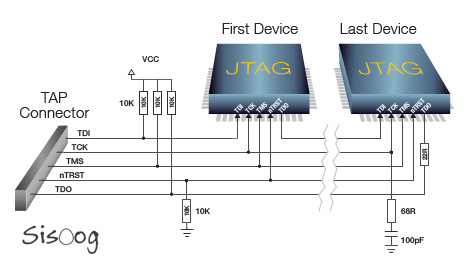

مشخصات الکتریکی

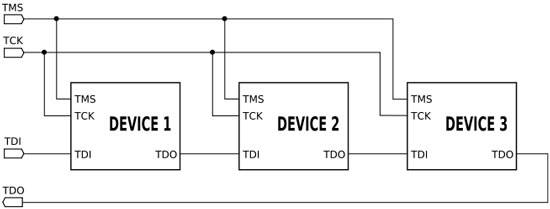

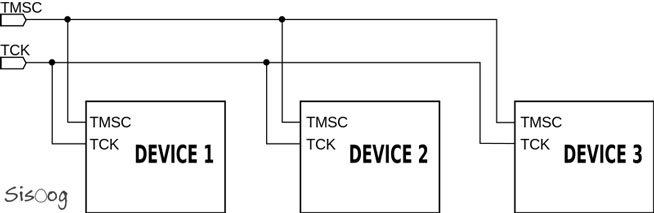

رابطهای چهار و پنج پین به گونهای طراحی شدهاند که در صورت برآورده شدن شرایطی خاص، چندین تراشه میتوانند به صورت سری همانند شکل زیر به همدیگر وصل شوند و با همین توپولوژی نیز به صورت همزمان چندین تراشهی مختلف مانند میکروکنترلر یا FPGA را پروگرام کنیم.

(Daisy-chained JTAG (IEEE 1149.1

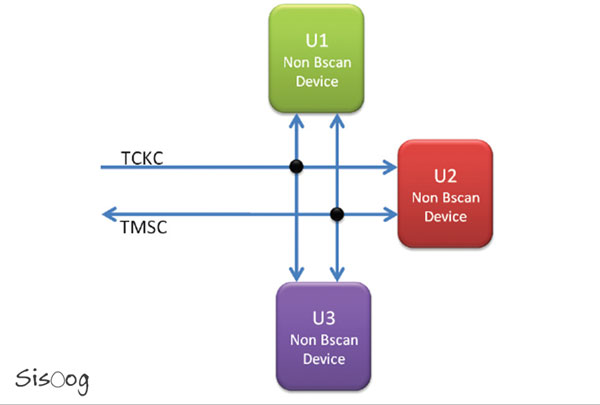

رابط دو پین به گونهای طراحی شده است که میتوان چندین تراشه را در یک توپولوژی ستاره متصل کرد.

در هر دو حالت بالا، یک پروب آزمایش فقط به یک “پورت JTAG” وصل میشود تا به تمام تراشههای موجود دسترسی داشته باشد.

پینهای پروتکل jtag

- (TDI (Test Data In

- (TDO (Test Data Out

- (TCK (Test Clock

- (TMS (Test Mode Select

- TRST (Test Reset) optional

پین TRST یک پین ریست active-low برای تست میباشد. این پین معمولا آسنکرون است، اما با توجه به تراشه میتواند سنکرون نیز باشد. به طور کلی برخی عملیات در JTAG وجود دارد که میتوانیم با استفاده از این عملیات فقط بخشهایی از پردازنده را ریست کنیم.

از آنجا که فقط یک خط داده وجود دارد پس پروتکل سریال است. کلاک ورودی پین TCK میباشد و یک بیت داده با هر لبه بالارونده کلاک، از TDI به TDO منتقل میشود.

پروتکل JTAG میتواند دستورالعملهای متفاوتی را بر روی تراشه بارگذاری کند، با استفاده از این دستورالعملها میتواند نوع تراشه را با استفاده از ID درون تراشه مشخص کند، عملکرد تراشه را دستکاری کند، تراشه را در ساختار و توپولوژی Daisy-chained JTAG بایپس (bypass) کند و بسیاری از کارهای دیگر.

حداکثر فرکانس کاری TCK، بسته به اینکه چه نوع تراشههایی در توپولوژی Daisy-chained JTAG وجود دارد میتواند متفاوت باشد، به طور کلی باید کمترین فرکانس مربوط به تراشهها انتخاب شود تا عملکرد صحیحی داشته باشیم. اما معمولا فرکانس کاری عددی بین 10 تا 100 مگاهرتز میباشد. همچنین فرکانس TCK با توجه به چیدمان برد و آدابتور JTAG میتواند متفاوت باشد.

پروتکل JTAG با استفاده از TMS و یک ساختار State Machine، میتواند در مدهای مختلف کاری قرار بگیرد و به نواحی مختلف دسترسی داشته باشد.

(Reduced pin count JTAG (IEEE 1149.7

یکی از عیبهای که بعضی از افراد نسبت به JTAG خرده میگیرند، تعداد پینهای زیاد این پروتکل میباشد. اما در استانداردهایی تعداد پینها به 2 پین تقلیل یافته است که در ادامه به معرفی آن میپردازیم.

پینهای پروتکل jtag با پینهای کاهش یافته

- (TMSC (Test Serial Data

- (TCKC (Test Clock

رابط دو سیمه باعث میشود که ما بتوانیم دیوایسهای مختلف را با استفاده از توپولوژی ستاره به هم متصل کنیم. توپولوژی ستاره این امکان را میدهد که قسمتهایی از سیستم یا بعضی از دیوایسها خاموش شوند، اما در توپولوژی Daisy-chained JTAG همچین امکانی وجود ندارد.

هدف و تمرکز این مقاله روی این موضوع بود که کلیت و قابلیتهای پروتکل JTAG را ارائه بدهد و نه تشریح عملکرد پروتکل. امیدواریم که بتوانید از این قابلیتهای خاص پروتکل JTAG به صورت عملی در پروژههایتان استفاده کنید.

نویسنده شو !

سیسوگ با افتخار فضایی برای اشتراک گذاری دانش شماست. برای ما مقاله بنویسید.