ساختار for در زبان VHDL

قسمت 19for;

در قسمت هجدهم از آموزش FPGA با شیفت رجیستر آشنا شدیم و مفصلا به تعریف آن پرداختیم، ساختارهای مختلف آن را با هم دیدیدم، همچنین عملکرد انواع شیفت رجیسترها را بررسی کردیم و آنها را با رجیسترها مقایسه کردیم. در نهایت هم یک نوع از آن شیفت رجیسترها را یک بار با شیفت به راست و بار دیگر با شیفت به چپ با استفاده از کد VHDL توصیف کردیم.

اما اگر میخواستیم عرض بیت شیفت رجیستر را افزایش بدهیم با یک مشکل جدی روبهرو بودیم، و باید تعداد خطوط کدی که مینوشتیم بیشتر و بیشتر میشد که این موضوع برای شیفت رجیسترهایی با تعداد بیت زیاد اذیتکننده است.

چندین راه برای اینکه بتوانیم این مشکل را هموار کنیم وجود دارد یک راه استفاده از عملگرهاست، اما چون هنوز با عملگرها در زبان VHDL آشنا نیستیم نمیتوانیم از آنها استفاده کنیم. شما بعدا که با این عملگرها آشنا شدید، میتوانید خودتان کد موردنظر را بنویسید.

راه دیگر استفاده از ساختار for در زبان VHDL میباشد که ابتدا باید با این ساختار آشنا شویم و پس از اینکه با عملکرد این ساختار آشنا شدیم کدهای قسمت قبل را با این ساختار توصیف کنیم.

اگر با FPGA آشنایی ندارید اول مقاله FPGA چیست؟ را مطالعه نمایید.

ساختار for در زبان VHDL

اگر قبلا با زبانهای برنامهنویسی دست و پنجه نرم کرده باشید به احتمال زیاد با for آشنا هستید. ما نیز قصد نداریم که به تشریح حلقهها و انواع آنها بپردازیم بلکه توضیحاتی مختصر میدهیم تا هم یادآوری شود و هم بتوانیم ادامه صحبتمان را بهتر ارائه بدهیم تا موضوع به خوبی تفهیم شود.

مثلا اگر میخواستیم در خانههای یک آرایه بنویسیم دو راه وجود داشت، یک راه اینکه با استفاده از اندیس آن آرایه در هر خط کد مقادیری را به خانههای آرابه اختصاص بدهیم که این کار اگر تعداد خانههای آرایه زیاد باشد کاری حوصلهبر و وقتگیر است.

راه دیگر این بود که با استفاده از حلقه for و تعیین شرطی متناسب با خانههای آرایه، فقط با چند خط در خانههای آرایه بنویسیم که راهی معقولتر و به نسبت خیلی راحتتر است.

ما نیز قصد داریم که با همین ایده کدهای جلسه قبل را بهینهتر کنیم و تا هر مقدار که بخواهیم با تغییراتی بسیار کوچکی عرض بیت شیفت رجیستر را افزایش بدهیم.

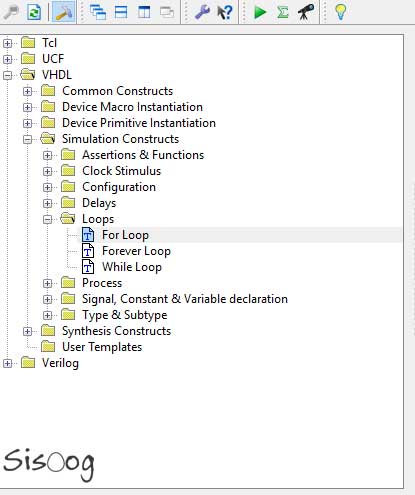

برای دسترسی به الگوی ساختار for در زبان VHDL میتوانیم همانند تصویر زیر در نرمافزار ISE، ابتدا روی علامت لامپ روشن کلیک کنید و سپس طبق تصویر، For Loop را از دسته Loops انتخاب کنید تا به الگویی که در ادامه کد آن آورده میشود برسید.

|

1 2 3 4 |

for <variable_name> in <lower_limit> to <upper_limit> loop <statement>; <statement>; end loop; |

در کد بالا به جای variable_name، باید از یک اندیس استفاده کنیم که عمل شمارش را برای ما انجام میدهد.

معمولا اسم این اندیس را i میگذاریم و بعدا در کد اصلی از همین اندیس کمک خواهیم گرفت.

به جای lower_limit از یک عدد صحیح مثبت به عنوان کران پایین اندیس i و به جای upper_limit از یک عدد صحیح مثبت به عنوان کران بالای اندیس i استفاده میکنیم.

statementها هم همان ارجاعات هستند.

در ادامه کدهای قسمت هجدهم را با ساختار for بازنویسی خواهیم کرد تا موضوعات بیان شده را به خوبی درک کنید.

کد زیر همان شیفت رجیستری است که در قسمت قبل عمل شیفت به راست را انجام میداد:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 |

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; entity Shift_Register is Port ( Input : in STD_LOGIC; Clock : in STD_LOGIC; Output : out unsigned (7 downto 0) ); end Shift_Register; architecture Behavioral of Shift_Register is signal Middle : unsigned (7 downto 0) := (others =>'0'); begin Output <= Middle; process(clock) begin if rising_edge(clock) then Middle(7) <= Input; for i in 0 to 6 loop Middle(i) <= Middle(i+1); end loop; end if; end process; end Behavioral; |

کد زیر همان شیفت رجیستری است که در قسمت قبل عمل شیفت به چپ را انجام میداد.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 |

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; entity Shift_Register is Port ( Input : in STD_LOGIC; Clock : in STD_LOGIC; Output : out unsigned (7 downto 0) ); end Shift_Register; architecture Behavioral of Shift_Register is signal Middle : unsigned (7 downto 0) := (others =>'0'); begin Output <= Middle; process(clock) begin if rising_edge(clock) then Middle(0) <= Input; for i in 0 to 6 loop Middle(i+1) <= Middle(i); end loop; end if; end process; end Behavioral; |

کدهای بالا را با استفاده از generic میتوانید بهینهتر نیز بنویسید که این موضوع را چون قبلا به آن پرداختیم به عهده خودتان میگذاریم. در قسمت بیستم در مورد عملگرها صحبت خواهیم کرد.

سیسوگ با افتخار فضایی برای اشتراک گذاری دانش شماست. برای ما مقاله بنویسید.