نحوهی نوشتن ریست در FPGAهای شرکت Xilinx

قسمت 15در قسمت چهاردهم از آموزش FPGA در مورد اینکه عملکرد ریست چیست و دقیقا چه کاری انجام میدهد مفصلا صحبت کردیم. سپس به صورت خیلی جزئیتر در مورد عملکرد ریست در FPGA صحبت کردیم و عملکرد آن را توضیح دادیم و گفتیم که در FPGA ریست را به دو صورت سنکرون و آسنکرون میتوان پیادهسازی کرد و نهایتا با استفاده از زبان VHDL، ریست سنکرون و آسنکرون را توصیف کردیم.

در این قسمت ریست را با جزئیات بیشتری بررسی خواهیم کرد و نکاتی را به شما خواهیم گفت که به احتمال زیاد برای شما جدید خواهند بود. شما همچنین با استفاده از این نکات و رعایت کردن آنها در پروژههایتان، هم مدار بهینهتری خواهید داشت، هم سرعت مدارتان بالاتر خواهد رفت و هم از منابع کمتری استفاده خواهید کرد، چه چیزی بهتر از این!

اجازه بدهید ابتدا کد جلسه قبل را دوباره بازنویسی کنیم تا درباره آن بهتر بتوانیم توضیح بدهیم.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 |

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity Flip_Flop is Port ( D : in STD_LOGIC; Clock : in STD_LOGIC; Reset : in STD_LOGIC; Q : out STD_LOGIC ); end Flip_Flop; architecture Behavioral of Flip_Flop is begin process(Clock) begin if rising_edge(Clock) then Q <= D; if (Reset = '1') then Q <= '0'; end if; end if; end process; end Behavioral |

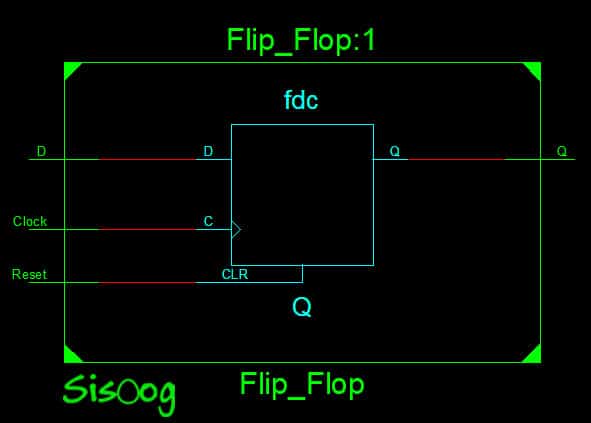

همانطور که از قسمت قبل میدانید، کد بالا توصیف ریست سنکرون است. اکنون قصد داریم که بررسی کنیم که ریست سنکرون با این نحوه کدنویسی به چه صورت در FPGA پیادهسازی میشود. به مدار زیر توجه کنید:

مدار پیادهسازی شده بسیار ساده میباشد و یک فلیپفلاپ میباشد که شما قبلا تقریبا همین مدار را دیده بودید اما الان یک چیز دیگر به نام ریست به همان فلیپفلاپ اضافه شده است. عملکرد ریست را هم که از قسمت قبل میدانید و نیاز به هیچ توضیح اضافی نیست.

حال بیایید یک تغییر کوچک در کد بدهیم و ببینیم که چه اتفاقی در مداری که درون FPGA پیادهسازی میشود خواهد افتاد.

ما در کد بالا شرط زیر را نوشتیم:

|

1 |

if (Reset = '1') |

اکنون قصد داریم فقط با یک تغییر کوچک همین یک خط کد را در کد اصلی به صورت زیر تغییر دهیم:

|

1 |

if (Reset = '0') |

اگر توجه کنید فقط مقدار 1 را با مقدار 0 جایگزین کردیم، یعنی سیگنال ریست با مقدار 0 مقایسه میشود و هر موقع که ریست برابر 0 بود عمل موردنظر انجام میشود در صورتی که قبلا به این صورت بود که سیگنال ریست با مقدار 1 مقایسه میشد و هر موقع ریست برابر با 1 بود عمل موردنظر انجام میشد.

نهایتا کد ما به صورت زیر تغییر میکند:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 |

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity Flip_Flop is Port ( D : in STD_LOGIC; Clock : in STD_LOGIC; Reset : in STD_LOGIC; Q : out STD_LOGIC ); end Flip_Flop; architecture Behavioral of Flip_Flop is begin process(Clock) begin if rising_edge(Clock) then Q <= D; if (Reset = '0') then Q <= '0'; end if; end if; end process; end Behavioral; |

باید یک بار دیگر مدار پیادهسازی شده در FPGA را درون نرمافزار ISE باز کنیم تا ببینیم با یک تغییر کوچک در کد، چه تغییری در سختافزار به وجود آمده است!

به مدار زیر توجه کنید:

همانطور که مشاهده میکنید یک تغییر بسیار کوچک در مدار پیادهسازی شده به وجود آمده است، این تغییر کوچک، اضافه شدن یک گیت نات به مدار قبلی است. اما دلیل این موضوع چیست؟ دلیل این موضوع چیزی نیست به جز توضیح کلی زیر:

آیا مورد ذکر شده میتواند باعث به وجود آمدن مشکل خاص یا حادی شود؟ برای پاسخ به این سوال ابتدا شما را با توضیحاتی آشنا خواهیم کرد در نهایت یک سری نتایج کلی در این رابطه ارائه خواهیم داد.

وقتی سیگنال ریست را با مقدار 0 مقایسه میکنیم دقیقا همین اتفاق رخ میدهد، و یک گیت نات که خود یک مدار ترکیبی میباشد قبل از ورودی ریست فلیپفلاپ قرار میگیرد که همین تغییر کوچک باعث کاهش سرعت مدار خواهد شد.

جدای از بحث ریست اگر در بین عناصر یا مدارات ترتیبی، یک مدار ترکیبی قرار بگیرد، سرعت مدار کاهش پیدا میکند که این موضوع اصلا خوشایند و مطلوب ما نیست و گاها به خاطر سرعت بیشتر ما حاضر هستیم تراشهی خود را عوض کنیم که این موضوع در تولید انبوه هزینهی گزافی را به دنبال خواهد داشت.

شاید با خودتان فکر کنید که مگر یک گیت نات تا چه اندازه میتواند سرعت مدار را کاهش دهد که تا این حد مته به خشخاش میگذاریم و میگوییم که از انجام این کارها باید به شدت اجتناب ورزید؟

در پاسخ باید گفت که اولا فقط یک گیت نات نیست و شما با نادیده گرفتن این موضوعات، در مواردی مشابه همین اشتباه را تکرار میکنید و آن موقع تاخیری چندین برابر یک گیت نات میتواند به وجود بیاید و به سرعت دلخواه و مطلوبتان نرسید.

به علاوه در نظر بگیرید که با رعایت کردن این نکات تا چه اندازه میتوانیم در مصرف منابع درونی FPGA صرفهجویی کنیم و همچنین مدار بهینهتر و با قابلیت اطمینان بیشتری داشته باشیم.

با مواردی از این قبیل که میتوانند سرعت مدار را کاهش دهند یا منابعی زیادی از FPGA مصرف کنند، در روند این مجموعه آموزشی آشنا خواهیم شد.

به طور کلی رعایت کردن موارد ذکر شده سه مورد زیر را نتیجه خواهد داد:

- سرعت بالاتر

- صرفهجویی در استفاده از منابع درونی FPGA

- قابلیت اطمینان بیشتر و بهینهگی مدار

اگرچه مدارات ترکیبی جز جداییناپذیر و لاینفک یک مدار دیجیتال هستند، اما تا حد امکان باید از استفاده از این مدارات در یک طراحی دیجیتال اجتناب ورزید.

در قسمت شانزدهم دوباره در رابطه با موضوع ریست صحبت خواهیم کرد و دوباره نکاتی جدید را به شما آموزش خواهیم داد، پس با ما همراه باشید.

سیسوگ با افتخار فضایی برای اشتراک گذاری دانش شماست. برای ما مقاله بنویسید.