در قسمت دهم از آموزش FPGA به طور کامل با ساختار شرطی if آشنا شدیم و همهی قابلیتهای این ساختار را با استفاده از مثال انکودر اولویتدار به طور کامل بررسی کردیم.

در این قسمت قصد داریم ساختار شرطی case را بررسی کنیم، و این ساختار را با ساختار شرطی if مقایسه کنیم. در نهایت مزایا و معایب هر کدام را نسبت به دیگری بیان خواهیم کرد.

در قسمتهای قبلی مثالهایی که بیان کردیم عمدتا مدارات ترکیبی مانند مالتیپلکسر، انکودر و … بودند که همهی ما حداقل از دوران دانشگاه تا حدودی با این مدارات آشنا هستیم. در بسیاری از کتابها نیز سعی میشود که اصول اولیه زبان VHDL با استفاده از توصیف همین مدارات آموزش داده شود، ما نیز از این قاعده مستثنی نبودیم و سعی کردیم همین روند را دنبال کنیم. اگرچه همین مدارات ذکر شده، المانهای پایه و ضروری در طراحی مدارات دیجیتال میباشند، اما شاید شما از این روند خسته شده باشید و منتظر مثالهای متنوعتری باشید. نگران نباشید، از این قسمت به بعد کمکم مثالها عوض خواهند شد و همچنین با کدنویسی اصولی آشنا خواهید شد.

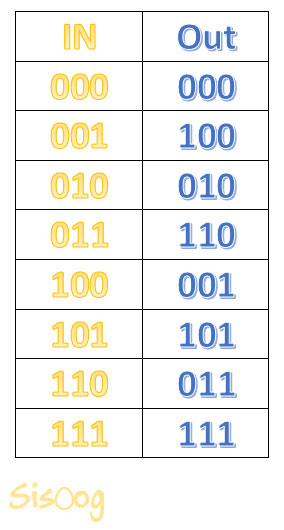

فرض کنید مداری وجود دارد که وقتی یک ورودی چند بیتی به آن اعمال میشود، ترتیب بیتها را به نحوی که ما تعیین میکنیم تغییر میدهد. برای سادگی در نظر بگیرید که بیتها به نحوی تغییر میکنند که کمارزشترین بیت جایش را به باارزشترین بیت میدهد، به همین ترتیب بیتها جابهجا میشوند تا اینکه با ارزشترین بیت جایش را به کم ارزشترین بیت میدهد. نحوهی جابهجایی بیتها را میتوانید در تصویر زیر مشاهده کنید.

حال میخواهیم عملکرد جدول بالا را با استفاده از ساختار شرطی case در زبان VHDL توصیف کنیم. ابتدا کد مربوطه را خواهیم نوشت، سپس توضیحاتی در مورد عملکرد و سینتکس کد خواهیم داد.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 |

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; entity MSB_LSB is Port ( I : in unsigned (2 downto 0); O : out unsigned (2 downto 0) ); end MSB_LSB; architecture Behavioral of MSB_LSB is begin process(I) begin case I is when "000" => O <= "000"; when "001" => O <= "100"; when "010" => O <= "010"; when "011" => O <= "110"; when "100" => O <= "001"; when "101" => O <= "101"; when "110" => O <= "011"; when others => O <= "111"; end case; end process; end Behavioral; |

همانطور که در کد بالا مشاهده میکنید بعد از کلمه کلیدی case، سیگنالی که قرار است روی آن شرط بگذاریم (i) نوشته خواهد شد. پس از سیگنال شرط، کلمه کلیدی is قرار خواهد گرفت. اکنون با استفاده از کلمه کلیدی when، مقادیر مختلف را روی سیگنال شرط قرار خواهیم داد. بعد از اینکه مقادیر مختلف را روی سیگنال شرط قرار دادیم، نوبت آن است که ارجاعات متناظر با شرط موردنظر را بنویسیم. به همین ترتیب ابتدا شرط مربوطه، و سپس ارجاعات متناظر با آن را مینویسیم. در نهایت این ساختار با عبارت کلیدی end case به پایان میرسد.

در واقع عبارت when others نه تنها حالت “I=”111 را شامل میشود، بلکه به چندین حالت دیگر نیز اشاره میکند. اجازه بدهید در ادامه مفصلتر در باب این موضوع صحبت کنیم.

3 حالتی که قابلیت پیادهسازی دارند عبارتند از:

تا به حال ما دو حالت اول را شناختیم و در مثالهای مختلف از این حالات استفاده کردیم، در قسمتهای پیشرو مفصلا در مورد حالت z صحبت خواهیم کرد. الان فقط به این حالت اشاره کردیم تا بتوانیم در ادامه توضیحاتمان را کامل کنیم.

در مثال ما چون ورودی 3 بیتی است، پس 729 حالت متفاوت میتواند وجود داشته باشد، از بین تمامی این حالات 27 حالت قابلیت پیادهسازی را دارند. اکنون اگر حالتهایی که حداقل یکی از بیتها شامل z میشود را در نظر نگیریم؛ جمعا 8 حالت باقی میماند. 7 حالت از این 8 حالت را در شرطهای متوالی با استفاده از کلمه کلیدی when، قبل از عبارت when others پوشش دادیم. تنها یک حالت دیگر باقی میماند، ما همیشه در هر مثالی آخرین حالت موردنظر را در یکی از حالتهای when others در نظر خواهیم گرفت.

در یک جمعبندی کلی میتوان گفت در مثال بالا when others به 722 حالت اشاره میکند که تنها یکی از این حالات مدنظر ما است.

هر کدام از دو ساختار شرطی که در محیط ترتیبی شناختیم (یعنی ساختار شرطی if و case) متناسب با سیگنال شرط، میتوانند مورد استفاده قرار بگیرند. برای اینکه بهتر بدانید چه موقع از کدام یک از این ساختارهای شرطی استفاده کنید به توضیحات زیر توجه کنید.

در ساختار شرطی case، فقط میتوانیم از حالت مساوی بودن استفاده کنیم، به عبارتی دیگر فقط عملگر مساوی (=) میتواند روی سیگنال شرط قرار بگیرد. اما در ساختار شرطی if، هر عملگری میتواند روی سیگنال شرط قرار بگیرد، همچنین میتوانیم ترکیب چندین شرط مختلف را نیز داشته باشیم.

اینطور به نظر میرسد که ساختار شرطی if، کاملتر و جامعتر از ساختار شرطی case است؟ بله ساختار شرطی if کاملتر و جامعتر است، اگر ما در کدمان فقط از if استفاده کنیم با هیچ محدودیتی روبهرو نمیشویم و میتوانیم هر حالتی را در کدمان به خوبی پوشش بدهیم. اما همیشه همه چیز به این خوبیها نیست و گاها مشکلاتی برایمان ایجاد خواهد شد که با رعایت کردن نکاتی که در ادامه خواهیم گفت، این مشکلات برطرف خواهند شد.

اجازه بدهید قبل از اینکه به خود مشکل بپردازیم گذری بر این داشته باشیم که ساختار شرطی if و ساختار شرطی case چگونه در FPGA پیادهسازی میشوند. در صورتی که شما بدانید این ساختارها چگونه در FPGA پیادهسازی میشوند، به احتمال زیاد حدس بزنید که چرا با اینکه میدانیم ساختار شرطی if قابلیت بیشتری دارد ولی همیشه نباید از این ساختار استفاده کنیم.

وقتی از ساختار شرطی case استفاده میکنیم تمامی شرطها همزمان با یکدیگر بررسی میشوند و تاخیر در حالت حداقل خود میباشد. اما زمانی که از ساختار شرطی if استفاده میکنیم، شرطها به ترتیب از بالا به پایین مورد بررسی قرار خواهند گرفت و تاخیر از مقدار حداقلی که در ساختار شرطی case داشتیم، مقداری بیشتر خواهد بود.

مشکل چه زمانی ایجاد خواهد شد؟ ممکن است ما الگوریتمی داشته باشیم که وقتی درون FPGA پیادهسازی شد، نیاز باشد با کلاک 100M کار کند تا خواسته مسئله برآورده شود، یا به عبارتی دیگر محاسبات الگوریتم به درستی انجام شود. حال فرض کنید حداکثر کلاکی که ما مجاز هستیم به مدار اعمال کنیم (حداکثر کلاک قابل اعمال به مدار در نرمافزار قابل مشاهده است که در قسمتهای آتی در این مورد صحبت خواهیم کرد) مقداری کمتر از 100M است و اگر ما این کلاک را به مدار اعمال کنیم، محاسبات الگوریتم به درستی انجام نمیشود. یک راهحل این است که کد را بهینهتر بنویسیم تا به کلاک موردنظر برسیم، و یکی از این راههای بهینه شدن کد این است که تا جایی که میتوانیم به جای if، از case استفاده کنیم. پس از اینکه تغییرات لازم را انجام دادیم این احتمال وجود دارد که به کلاک موردنظر برسیم.

سلام ممنون خيلي استفاده بردم ممنون از سايت مفيدتون

مشكلي كه من داريم اينه كه شرطي كه بايد برسي كنم به سورت وكتور هست و خطا ميده كه بايد در دستور كيس براي آرايه سلكت انجام بشه بنظرتون بايد چكار كنم؟

سلام

با تشکر از آموزش خوبتون.

ببخشید در جلسه دهم گفته شد که ساختار شرطی if اگر دارای if_then باشد شرط ها بصورت موازی بررسی میشن ولی در جلسه یازدهم گفته شد که “در ساختار شرطی if، شرطها به ترتیب از بالا به پایین مورد بررسی قرار میگیرند”

کدوم درسته؟

سلام مهرناز جان.

ببینید اگر شما ifها را به صورت جداگانه بنویسید، و هیچ else یا elsif نباشد، در این صورت به صورت موازی بررسی میشوند. دلیلش هم این است که شرطها از هم مستقل هستند.

اما اگر در ساختار شرطی if از else یا elsif استفاده بکنیم، آن موقع بررسی به ترتیب از بالا به پایین است.

توضیح مختصر و مفیدش این بود، اگر باز جایی مشکل داشتید بپرسید.

متوجه شدم

خیلی ممنون

???

خیلی ساده و روان . به من که خیلی کمک کرد .

فقط امیدوارم آموزشتون ادامه داشته باشه و تمام نشه اینجا .

ممنون، نظر لطف شماست فرید عزیز. آموزش FPGA ادامهدار خواهد بود و در نهایت به MicroBlaze ،Zynq و HLS ختم خواهد شد.

با سلام و تشکر بینهایت بابت مطالب اموزشی تون که کاملا مشخصه زمان صرف کردید چون بسیار عالی و قابل فهم نوشته شده . من به اموزش میکرو بلیز به شدت نیاز دارم و بی صبرانه منتظرم که اموزشش رو بذارید و پیشاپیش ممنونم .

سلام دوست عزیز. سپاس از توجهتان. میکروبلیز چیز خاصی نداره، لازمش دونستن زبان C و سینتکسهایی هست که براش وجود داره و جانمایی اون بر روی FPGA هستش. بقیش میشه همون میکروکنترلر دیگه.

سلام

مثل همیشه

عالی

مفید

کامل

منتظر ادامه آموزش ها هستیم

سلام امیر عزیز. خواهش میکنم؛ نظر لطف شماست.

سیسوگ با افتخار فضایی برای اشتراک گذاری دانش شماست. برای ما مقاله بنویسید.