توصیف عناصر حافظه با فلیپفلاپ

قسمت 13در قسمت دوازدهم از آموزش FPGA مفصلا در رابطه با عناصر حافظه در سیستمهای دیجیتال صحبت کردیم و به تشریح جزئیات آنها پرداختیم، در ادامه بیان کرده بودیم که این عناصر به دو دسته کلی با نامهای لچ و فلیپفلاپ تقسیم میشوند. نهایتا به شما توصیه کرده بودیم که در تمامی پیادهسازیها از فلیپفلاپ به جای لچ استفاده کنید و همچنین برای اولین بار مدارات ترتیبی در محیط Sequential را پیادهسازی کردیم.

در این قسمت قصد داریم بحث توصیف عناصر حافظه با فلیپفلاپ را که در قسمت قبل نا تمام گذاشتیم، از سر گرفته و توضیح بدهیم که چگونه کدی که در همان قسمت قبل نوشتیم در درون FPGA تبدیل به یک فلیپفلاپ شد.

اگر به خاطر داشته باشید، در قسمتهای اولیه آموزش FPGA گفته بودیم که سیگنالها تحت شرایطی درون FPGA تبدیل به سیم و تحت شرایط دیگری تبدیل به رجیستر میشوند، و به شما قول داده بودیم که بعدا در این مورد به طور کامل صحبت کنیم. پس با دقت به توضیحات زیر توجه کنید تا یک بار برای همیشه متوجه شوید که سیگنالها چه موقع تبدیل به سیم و چه موقع تبدیل به رجیستر میشوند.

در قسمتهای قبل، سیگنال را تعریف کردیم و همچنین در مثالی از کاربرد آن بهره بردیم، پس شما الان به خوبی میدانید که سیگنال چیست و در کجا میتوایم از آن استفاده کنیم. اما نکتهای که هنوز نمیدانید این است که سیگنال چه موقع تبدیل به سیم و چه موقع تبدیل به رجیستر میشود!

اجازه بدهید در ابتدا کد قسمت قبل را دوباره بازنویسی کنیم و توضیحاتی را در رابطه با این کد بیان کنیم، و نهایتا با نشان دادن مدار پیادهسازی شده در FPGA، ادعای خود مبنی بر اینکه اگر در محیط ترتیبی به سیگنالی ارجاع داده شود، آن سیگنال تبدیل به رجیستر میشود را ثابت کنیم.

با دقت به کد زیر توجه کنید:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 |

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity Flip_Flop is Port ( Clock : in STD_LOGIC; D : in STD_LOGIC; Q : out STD_LOGIC ); end Flip_Flop; architecture Behavioral of Flip_Flop is begin process (Clock) begin if rising_edge(Clock) then Q <= D; end if; end process; end Behavioral; |

در کد بالا ما یک پورت ورودی تک بیتی برای کلاک تعریف کردیم تا با تغییر آن process فعال شود، همچنین یک پورت ورودی تک بیتی و یک پورت خروجی تک بیتی نیز تعریف کردیم تا درون process و در محیط ترتیبی، پورت ورودی را به پورت خروجی ارجاع بدهیم، که ما این کار را در خط 19 ام کد انجام دادیم.

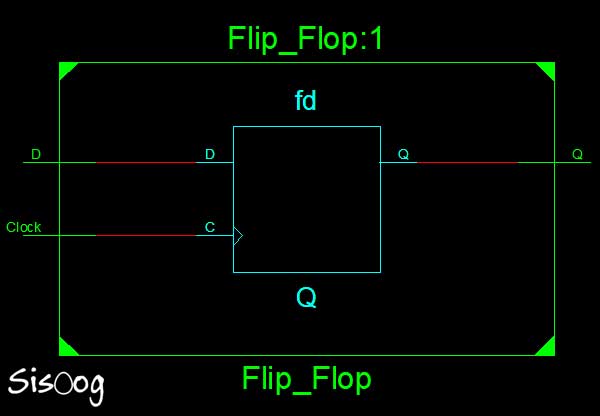

اکنون وقت آن رسیده است تا مشاهده کنیم که کد نوشته شده، در FPGA تبدیل به چه سختافزاری شده است. برای این کار ابتدا باید بر روی گزینهی View RTL Schematic دابل کلیک کرده و سپس بقیه مراحل را طبق همان مراحلی که در قسمت سوم بیان کردیم پیش بروید تا به مدار زیر برسید.

همانطور که در تصویر بالا مشاهده میکنید کد نوشته شده تبدیل به یک فلیپفلاپ در FPGA شد، اما دلیل آن چیست؟

قبل از اینکه به دلیل این موضوع بپردازیم که چرا کد نوشته شده، تبدیل به یک فلیپفلاپ در FPGA شد، باید یک توضیح مختصر در رابطه با فلیپفلاپ و رجیستر بیان کنیم.

پس اگر سیگنال ما تک بیتی باشد، وقتی در محیط ترتیبی و درون process به آن ارجاع داده میشود، آن سیگنال تبدیل به فلیپفلاپ میشود.

نکتهی دیگری که باید ذکر گردد این است که اگر در محیط ترتیبی و درون process به پورتی ارجاع داده شود، همهی شرایط سیگنالها برای این موضوع نیز صادق است، اگر توجه کرده باشید ما هم بعد از در کد نوشت شده به پورت ارجاع دادیم نه سیگنال، که البته این موضوع هیچ فرقی ندارد و تمامی شرایط یکسان خواهد بود.

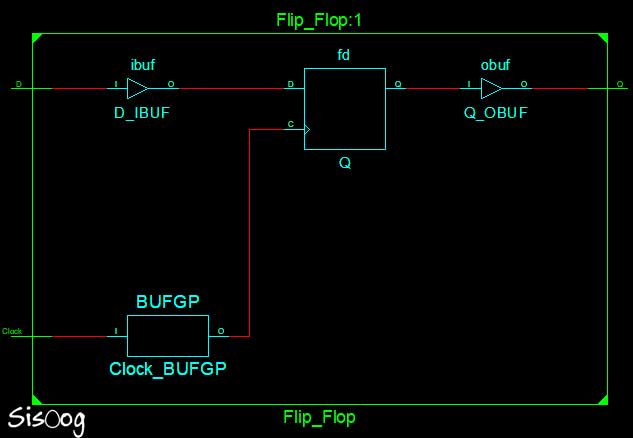

اما شماتیکی که در بالا مشاهده کردید دقیقا چیزی نیست که درون FPGA ساخته میشود، مداری که در FPGA پیادهسازی میشود کمی با شکل بالا متفاوت است و تمهیداتی دیگری را نیز شامل میشود. برای اینکه ببینید دقیقا درون FPGA چه چیزی پیادهسازی میشود باید تمامی مراحل بالا را بر روی گزینهی View Technology Schematic تکرار کنید تا به مدار زیر برسید:

شماتیک بالا همان چیزی است که درون FPGA پیادهسازی میشود، اگر توجه کنید در مواردی با تصویر قبلی متفاوت است.

چندین مورد تمهیدات اضافه شده است، از جمله بافر کلاک، بافر ورودی و بافر خروجی. قصد نداریم در مورد تمهیدات اضافه شده در این قسمت صحبت کنیم اما در همین حد بدانید که اگر قرار باشد پینی در FPGA به کلاک اختصاص داده شود، حتما باید آن پین قابلیت خاصی داشته باشد تا بتوانیم کلاک را به آن اعمال کنیم، به عبارتی دیگر به هر پین FPGA نمیتوان سیگنال کلاک را اعمال کرد.

در چندین قسمت مجزا مفصلا در مورد تمهیدات کلاک، پینهایی که میتوانند کلاک را دریافت کنند، نرمافزار چگونه تشخیص میدهد سیگنال کلاک، کدام سیگنال است، تولید کلاکهایی با فرکانسهای متفاوت و بسیاری از موارد دیگر صحبت خواهیم کرد.

در قسمت چهاردهم بحث مربوط به حافظهها را ادامه داده، و حافظههایی با قابلیت بیشتر را پیادهسازی خواهیم کرد. پس با ما همراه باشید.

سیسوگ با افتخار فضایی برای اشتراک گذاری دانش شماست. برای ما مقاله بنویسید.