آموزش میکروکنترلر STM32F4 – قسمت پنجم ;

در قسمت چهارم آموزش میکروکنترلر STM32F4 به ساختار باس پرداختیم. در این قسمت از آموزش میکروکنترلر STM32F4 به حافظه فلش و خواندن و نوشتن در حافظه میپردازیم. با سیسوگ همراه باشید.

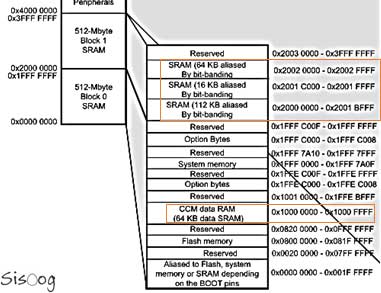

حافظه برنامه، حافظه داده، رجیسترها و درگاه های ورودی/خروجی همگی در فضای 4 گیگا بایتی آدرس دهی قرار گرفتهاند. بایتها در little endian ذخیره میشوند. فضای آدرس دهی حافظه به 8 بلوک اصلی با اندازه 512 مگابایت تقسیم شده است.

این میکروکنترلر دارای 4 کیلوبایت حافظه SRAM پشتیبانی و 256 کیلوبایت حافظه SRAM سیستم است. حافظه 256 کیلوبایتی از سه SRAM و یک SRAM جفت شده با پردازنده تشکیل شده است که به ترتیب دارای 112، 16 ، 64 و 64 کیلوبایت حافظه هستند. این حافظهها در شکل زیر با کاردهای نارنجی نشان داده شده است. این حافظه به شکل بایتی، نیمواژه (16 بیتی)، یا واژه کامل (32 بیتی) در دسترس است. خواندن و نوشتن در این حافظه، با سرعت پردازنده با صفر حالت انتظار، انجام میشود. این حافظه رم را میتوان تا 3 بخش تقسیم کرد:

مسترهای AHB میتوانند به شکل هم زمان به SRAM دسترسی داشته باشند (اترنت یا USB در راه (OTG) پرسرعت) برای مثال هم زمان که پردازنده با SRAM3 کار میکند اترنت میتواند با SRAM2 کار کند.

پردازنده میتواند به SRAMها از طریق باس سیستم یا کد I و D وقتی بوت از SRAM انجام میشود و بازنگاشت انتخاب شده است دسترسی داشته باشد.

رابط این حافظه، امکان دسترسی کد I و کد D باس AHB پردازنده را به حافظه فلش می دهد. امکان نوشتن و پاک کردن، و سازوکارهای محافظت از خواندن و نوشتن نیز فراهم است. ساختار این حافظه به این شکل است:

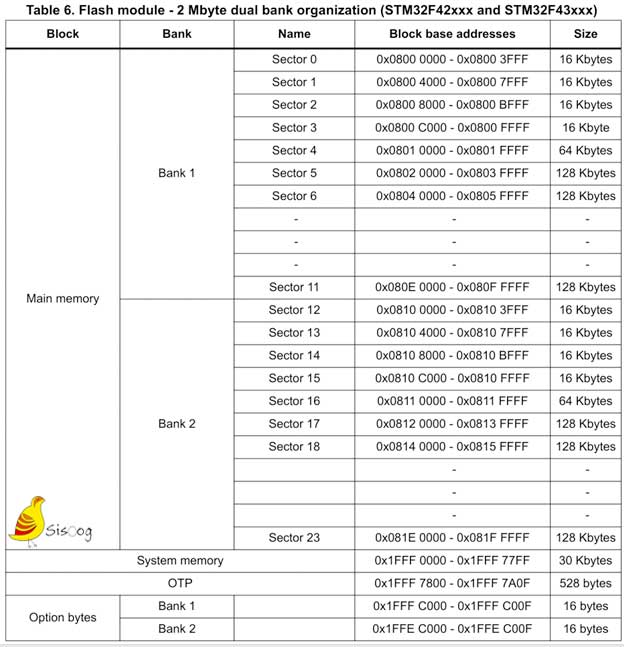

حافظه فلش داخلی تا 2 مگابایت حجم دارد و با ساختار دو بانکه دارای ویژگی خواندن/نوشتن است. پهنای باند خواندن 128 بیت است و برای نوشتن میتوان بایتی، نیم واژه یا واژه یا دو واژهای عمل کرد. امکان پاک کردن برشی، بانکی و انبوه برای هر دو بانک فراهم است.

حافظه فلش به شکل زیر سازماندهی شده است:

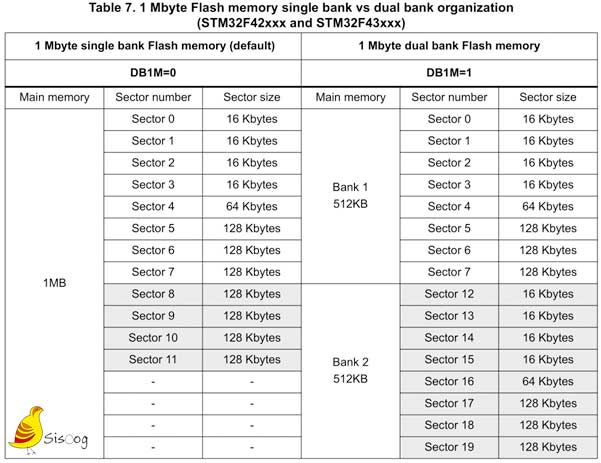

در دستگاههای دارای یک مگابایت حافظه ساختار کمی متفاوت است.

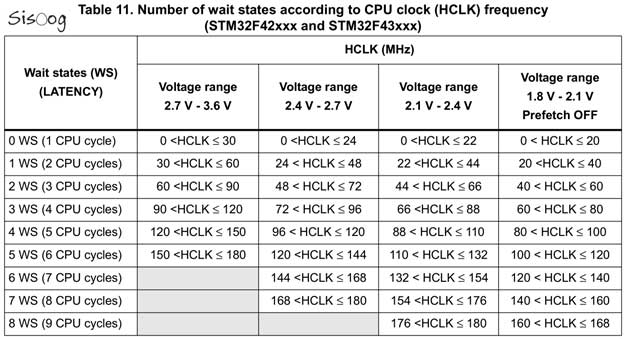

برای این که به درستی از فلش بخوانیم، تعداد حالتهای انتظار (یعنی پارامتر LATENCY) باید در رجیستر کنترل دسترسی به فلش (FLASH_ACR) مطابق فرکانس ساعت پردازنده HCLK و ولتاژ تغذیه دستگاه، برنامهریزی شود. برای ولتاژهای کمتر از 1/2 ولت باید بافر پیش واکشی (pre-fetch) غیرفعال شود. رابطه فرکانس ساعت و تعداد حالتهای انتظار در جدول زیر نشان داده شده است.

وقتی VOS[1:0] = ‘0x01’ ، بیشترین مقدار fHCLK برابر است با MHz 120

وقتی VOS[1:0] = ‘0x10’ ، بیشترین مقدار fHCLK برابر است با MHz 144. می توان با فعال کردن Over-drive تا MHz 168 هم رفت.

وقتی VOS[1:0] = ‘0x11’ ، بیشترین مقدار fHCLK برابر است با MHz 168 . می توان با فعال کردن Over-drive تا MHz 180 هم رفت.

در ولتاژ 1.8 تا 2.1 ولت نمی توان از حالت Over-drive استفاده کرد.

در قسمت پنجم آموزش میکروکنترلر STM32F4 به وقفهها خواهیم پرداخت. با سیسوگ همراه باشید.

واقعا ممنون کارتون حرف نداره

متشکر دوست عزیز 🙂

چقدر کوتاه بود … کاش مفصل تر توضیح میدادید!!!

درود برشما

امید دارم چیبی پر پول و سلامتی کامل داشته باشید.

دو پرسش :

1- STM32 برنامه ریخته شده روی آن را قفل کامل کرد که فقط بتوان میکرو را کامل پاک کرد و دو باره برنامه ریزی کرد؟؟

۲- همین کار برای stm8 ؟

در ۳۲ ها دیدیم ۴ حالت ( ۳ ) دارد ؛ گنگ بود ؛ یا بهتر بگویم من متوجه نشدم.

اگر لطف کنید توضیحی بدهید متشکر خواهم شد.

برای هر دو برنامه ریز

j link

st link /v2

با سپاس.

سیسوگ با افتخار فضایی برای اشتراک گذاری دانش شماست. برای ما مقاله بنویسید.