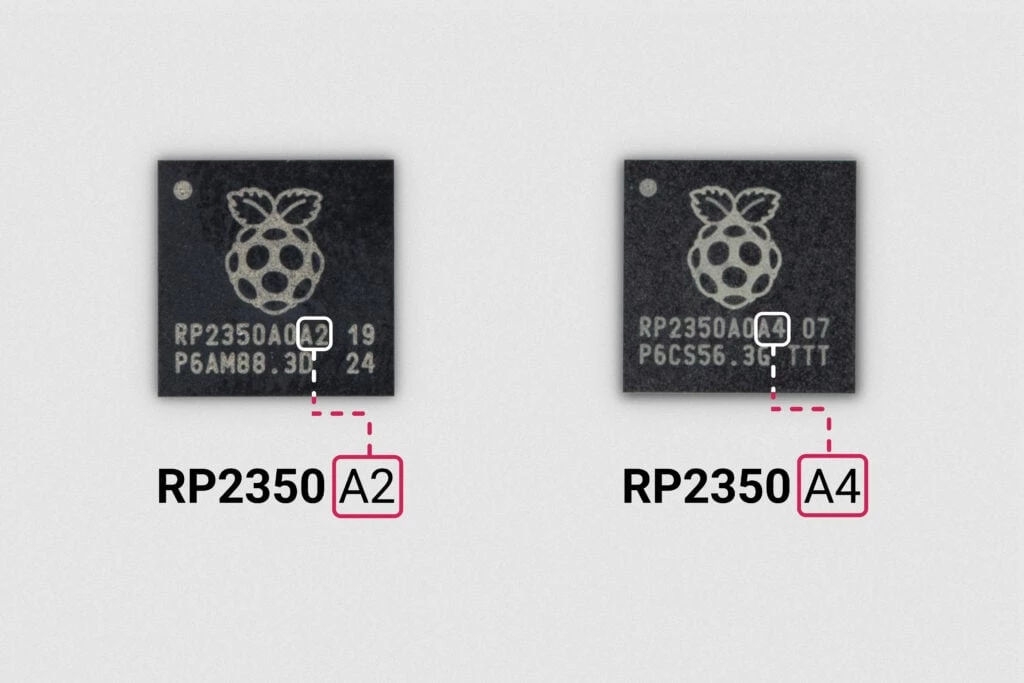

نسخهی A4 از RP2350 رونمایی شد: رفع باگهای مهم، بوترام جدید

تقریباً یک سال از تولد RP2350 نسل دوم میکروکنترلرهای رزبریپای میگذره. از اون موقع تا حالا، بیش از نیممیلیون برد Pico 2 و Pico 2 W عرضه شده و خود RP2350 هم راه خودش رو به دل کلی پروژه و محصول باز کرده؛ از نمایشگرهای صنعتی گرفته تا بردهای توسعه و حتی سینتیسایزرها!

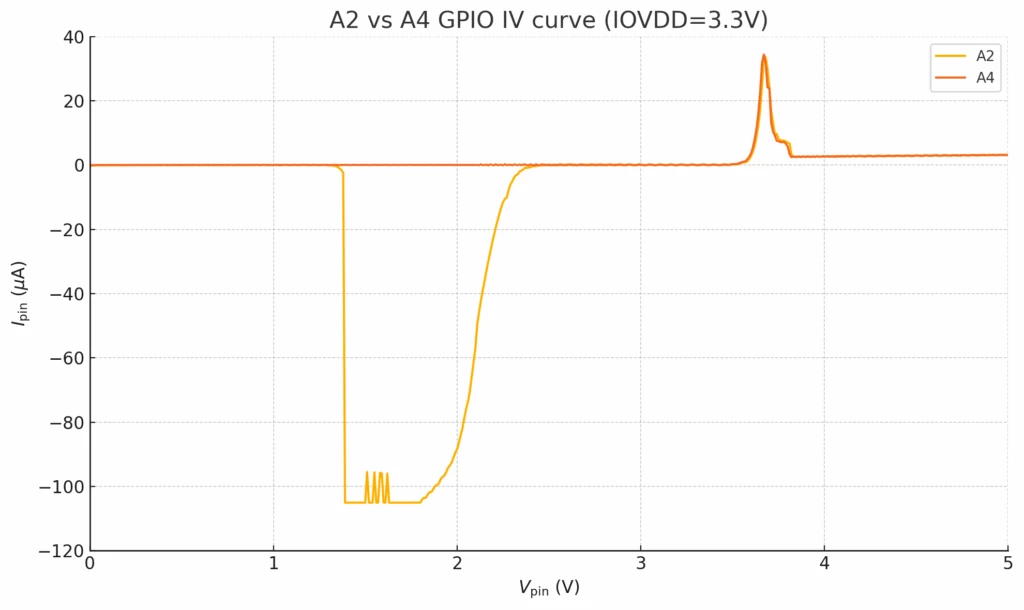

ولی خب، مثل هر چیپ سیلیکونی دیگهای، RP2350 از همون روز اول بینقص نبود. نسخهی ابتدایی که با عنوان A2 عرضه شد، چندتا اشکال ریز و درشت داشت. مثلاً طراحی پدهای GPIO یه مشکلی داشت که باعث میشد نتونن درست برن تو حالت high-impedance این همون ایراد معروف Erratum 9 ـه! از طرفی، توی چالش هک RP2350، چند مورد آسیبپذیری امنیتی هم توسط شرکتکنندهها پیدا شد.

و حالا خبر خوب! نسخهی جدیدی از این چیپ با stepping بهروزشدهی A4 منتشر شده که اکثر این ایرادها رو برطرف کرده و همین حالا آمادهی استفادهست.

<

همزمان با عرضهی نسخهی A4، یه سورپرایز دیگه هم اومد: معرفی رسمی RP2354! این مدل جدید در واقع نسخهی ارتقایافتهی RP2350 است، با همون پینآوت (کاملاً سازگار با RP2350A با 60 پین و RP2350B با 80 پین)، اما با یه ویژگی وسوسهانگیز، دو مگابایت فلش داخلی! یعنی بدون نیاز به حافظهی خارجی، فضای بیشتری برای کدت داری، اونم با فقط ۲۰ سنت بیشتر نسبت به مدل پایه.

و حالا بخش هیجانانگیزش برای بچههای امنیت و هک: یه دور جدید از مسابقهی Hacking Challenge هم راه افتاده! این بار جایزهی ۲۰ هزاردلاری درنظرگرفتن برای کسی که بتونه یه حملهی side-channel عملی روی کتابخونهی AES مقاومسازیشده انجام بده همون کتابخونهای که بوتلودر ازش استفاده میکنه.

توی A4 دقیقاً چی درست شده؟

اولازهمه، و از نظر بیشتر کاربرا شاید مهمترین اصلاح، همون Erratum 9 معروفه! یه تغییر کوچیک توی طراحی ماکروی پد اعمال کردیم که باعث شد اون نشتی ناخواسته در سمت مثبت پد حذف بشه. این همون نشتیای بود که باعث میشد نمودار جریان نسبت به ولتاژ تو نسخهی A2 یه افت شدید منفی نشون بده (نمودارش رو اگه دیده باشی، کاملاً مشخصه!).

نتیجهی این اصلاح اینه که دیگه لازم نیست مقاومت خارجی بزنی تا ورودیها رو pull-down کنی. البته اگه توی طراحیهات از قبل استفاده کردی، مشکلی نیست و میتونی همونطور نگهشون داری؛ ولی دیگه الزام نیست.

<

چند تا از آسیبپذیریهای امنیتی جدی هم توی نسخهی A4 برطرف شدن؛ اونم نه فقط یه پَچ ساده، بلکه با کلی تغییر اساسی و تدافعی جدید!

اشکالات شماره ۲۰، ۲۱ و ۲۴ توی Boot ROM مربوط به ضعفهای امنیتی بودن که توی چالش Hacking Challenge کشف شدن. تو نسخهی A4 این باگها کامل رفع شدن. تازه جدا از این، تیم توسعه حسابی دست به کار شده و کلی مکانیزم دفاعی جدید هم اضافه کرده تا احتمال سوءاستفادههای آینده تا جای ممکن کم بشه. فرصت رو هم غنیمت شمردن و یهسری باگ ریزتر تو عملکرد Boot ROM رو هم همونجا فیکس کردن.

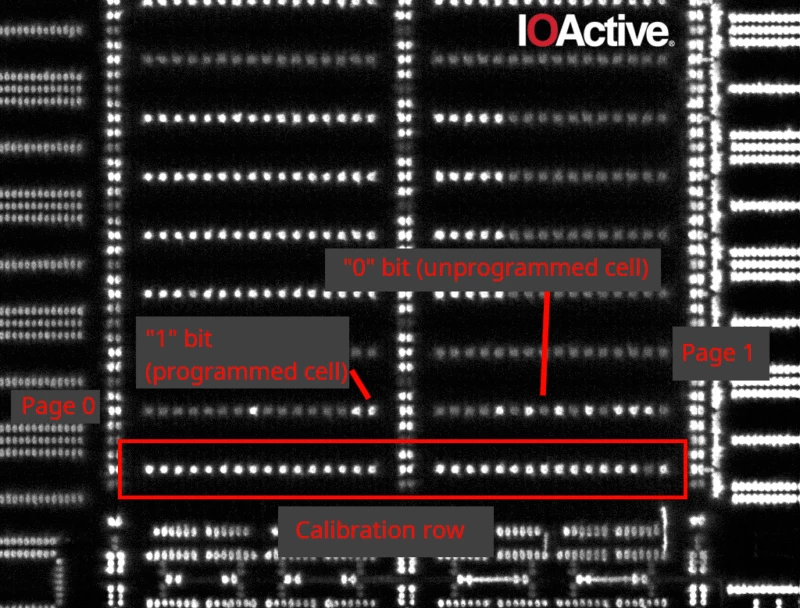

بریم سراغ اشکال شماره ۱۶، اینم یه مورد امنیتی بود که دوباره توسط هکرهای مسابقه کشف شد. مربوط میشه به رفتار حافظهی OTP (همون One-Time Programmable) موقعی که تغذیه قطع میشه، برای حل این مشکل، طراحی مدار اطراف OTP رو تغییر دادن و مشکل رو از ریشه حل کردن.

در نهایت، اشکال شماره ۳ که مربوط به رفتار رجیسترهای GPIO_NSMASK روی نسخههای ۶۰ پینی RP235x بود هم بالاخره درست شد.

چی توی A4 هنوز درست نشده؟

یکی از برندههای مسابقهی Hacking Challenge تونست یه آسیبپذیری عمیقتر رو تو خود ساختار بیتی OTP کشف کنه. با استفاده از یه تکنیک پیشرفتهای به اسم Passive Voltage Contrast، تونسته یه روش جالب برای خواندن حافظهی OTP پیدا کنه. حالا این روش دقیقاً چیکار میکنه؟

ایدهاش اینه: با تجهیزات تصویربرداری خاص (مثل میکروسکوپ الکترونی)، میشه تفاوت ولتاژی خیلی کوچیک بین بخشهای مختلف تراشه رو مشاهده کرد. تو حافظهی OTP، هر بیت معمولاً یه ساختار فیزیکی داره که اگه «برنامهریزی» شده باشه، ویژگی الکتریکیاش (مثلاً ظرفیت خازنی یا ولتاژ سطحی) فرق میکنه با حالتی که خام باشه.

حالا تو این حمله، اون فرد تونسته بفهمه که وقتی دو بیت کنار هم تو حافظه هستن، میتونه از ترکیبشون یه سیگنال بخونه که معادل OR منطقی بین اون دوتاست؛ این تکنیک مستقیماً مقدار هر بیت رو نمیخونه، ولی میتونه نتیجهی ترکیب OR دوتاییها رو بهدست بیاره. حالا اگه بتونی اینو برای بیتهای زیادی انجام بدی، و الگوریتمی طراحی کنی که از نتایج OR بین بیتهای مجاور، مقدار اصلی بیتها رو حدس بزنه، ممکنه در نهایت کل محتوای حافظهی OTP رو بازسازی کنی!

این آسیبپذیری هنوز تو نسخهی A4 رفع نشده. ولی قراره بهزودی یه اپلیکیشن نوت رسمی منتشر بشه که توش توضیح داده میشه چطور میتونید دادههای حساس رو به شکلی داخل OTP ذخیره کنید که در برابر این حمله، و حتی حملات شدیدتر احتمالی در آینده، تا حد خوبی مقاوم باشه.

چند تا از اشکالهای دیگه که امنیتی نبودن هم هنوز اصلاح نشدن، البته برای همهشون راهحلهای جایگزین (workaround) وجود داره و اصلاحشون نیاز به بازنویسی کامل طراحی داشته که فعلاً منطقی نبوده.

کالبدشکافی «metal spin»

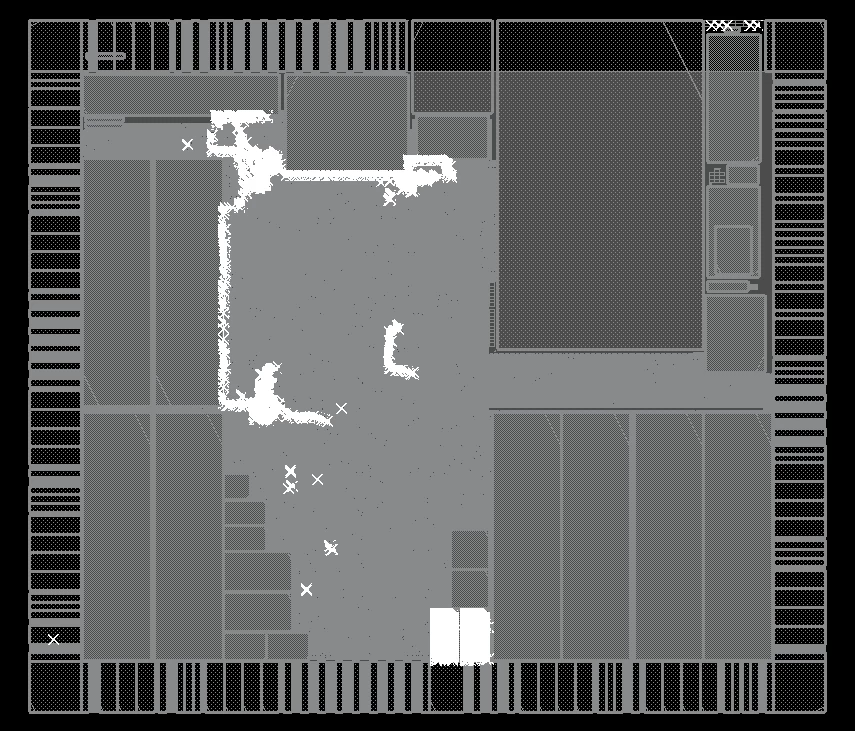

استپینگ A4 در واقع یه metal spin حساب میشه؛ یعنی چی؟ یعنی تغییرات عملکردی (مثل همون Boot ROM بهروزشده) از طریق دستکاری در لایههای فلزی تراشه انجام شده. این لایهها همون مسیرهایی هستن که گیتهای منطقی رو به هم وصل میکنن. پس بدون اینکه طراحی منطقی اصلی چیپ از نو بازسازی بشه، با تغییر مسیرهای داخلی، رفتار جدیدی براش تعریف کردن، یه جور بهروزرسانی سختافزاری!

تصویر زیر، دقیقاً نشون میده کدوم بخشهای تراشه توی A4 نسبت به نسخهی A2 فرق دارن. یه نگاه به پایین تراشه بنداز، اونجا یه تودهی متراکم از تغییراته — همونجاست که Boot ROM جدید جا خوش کرده.

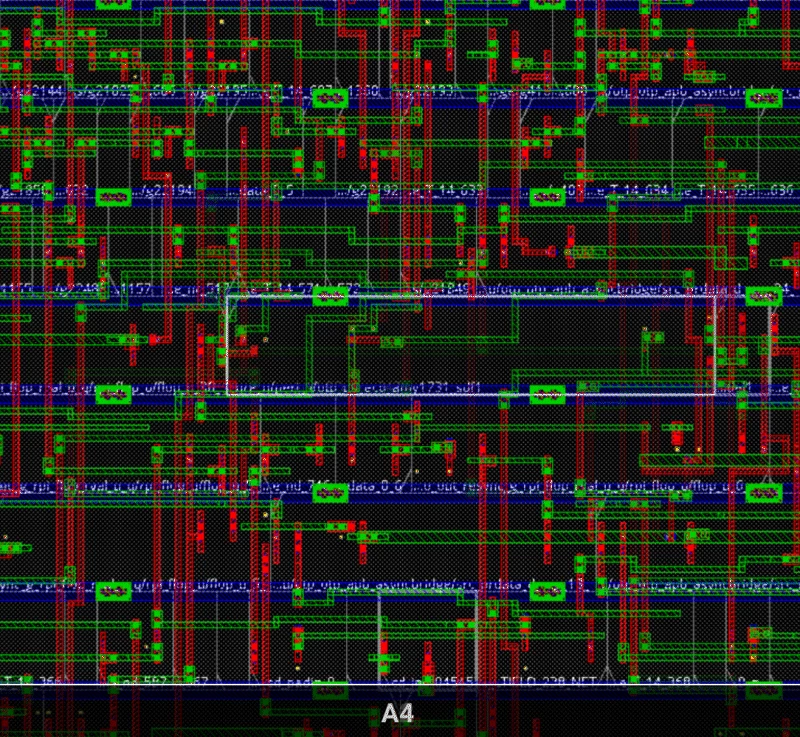

اگه یه کم زوم کنیم روی تراشه، میرسیم به یه نمای نزدیک از پیادهسازی یکی از اصلاحات، تو این تصویر خاص، داریم بخشی از سختسازی امنیتی مربوط به اشکال شماره ۱۶ رو میبینیم؛ همون مشکلی که وقتی برق وسط خوندن OTP قطع میشد، میتونست باعث نشت اطلاعات بشه.

از کجا بفهمم چیپی که دارم نسخهی A2 هست یا A4؟

خیلی سادهست، کافیه نگاهی بندازی به بالای پکیج چیپ. اونجا یه شناسه نوشته شده که steppingچیپ رو مشخص میکنه. مثلاً اگه A2 باشه، همونجا نوشته شده؛ اگه A4 باشه، اونم دقیقاً درج شده.

آیا نسخهی A4 از نظر نرمافزاری با A2 سازگاره؟

بله، صددرصد!

چیپ A4 بهطور کامل با A2 سازگاری نرمافزاری داره. البته یهسری تغییر جزئی توی نسخهی ۲.۲.۰ از Pico SDK و ابزار Picotool اعمال شده تا از stepping جدید A4 بهدرستی پشتیبانی کنن، ولی اگه کدتون برای A2 نوشته شده، بدون مشکل روی A4 هم کار میکنه.

منبع: raspberrypi.com

من اون دیوونهام که وقتی بورد روشن نمیشه، ذوق میکنم؛ یعنی یه شب تا صبح قراره با منبع تغذیه و لاجیک آنالایزر عشق کنم! آدما قهوه میخورن که بیدار بمونن، ولی من بیدار میمونم تا بفهمم این بورد چرا باهام قهر کرده! زندگی من یه لوپ بینهایته بین باگ و دیباگ... با چاشنی یه کم امید و یه عالمه دیوونگی!

مقالات بیشتر

سیسوگ با افتخار فضایی برای اشتراک گذاری دانش شماست. برای ما مقاله بنویسید.