بررسی مدار های ترکیبی و ترتیبی و بررسی الگو و ساختار کد در زبان VHDL - آموزش FPGA قسمت چهارم

قسمت 4در قسمت سوم از آموزش FPGA با نرم افزار ISE آشنا شدیم و در حد یک آشنایی اولیه توانستیم یک پروژه ایجاد کنیم، و یک کد بسیار ساده را نیز پیادهسازی کردیم. اکنون در این قسمت از آموزش FPGA قصد داریم که در ابتدا با ساختار و محیطهای مختلفی، که ما برای تولید سختافزار، در این محیطها، کد مینویسیم آشنا شویم و در نهایت یک مدار ترکیبی را با استقاده از کد توصیف کنیم. پس از اینکه در قسمتهای قبل به صورت مفصل در مورد ساختار FPGA صحبت کردیم و در قسمت قبلی نیز فقط به نوشتن یک کد ساده بسنده کردیم، دیگر وقتش رسیده است که به قسمتهای جذاب داستان نزدیک و نزدیکتر شویم. تقریبا از همین قسمت است که شما از حالت گنگ بودن و نامفهومی که شاید به خاطر آشنایی اولیه با FPGA و زبان VHDL است، رهایی خواهید جست، و دست و پنجه نرم کردن با این موجود به ظاهر خشک و عجیب و غریب برایتان هیجان انگیز خواهد بود. پس اجازه بدهید بدون فوت وقت به موضوع اصلی مورد بحث در این مقاله بپردازیم و با مدارات ترکیبی و ترتیبی در محیطهای Concurrent و Sequential آشنا شویم.

انواع مدار دیجیتال

در FPGA نیز محیطهایی برای طراحی اینگونه مدارها در نظر گرفته شده است که این انتخاب و انعطاف را به ما بدهد که در مواقع لزوم و بر حسب کارایی بتوانیم مدار مورد نظر را طراحی کنیم. اگر توجه کرده باشید امروزه تقریبا تمامی مداراتی که ما با آنها برخورد میکنیم مدارات ترتیبی هستند، و کمتر پروژهای را میبینیم که حداقل نوعی از حافظه، که خود نشانگر ترتیبی بودن مدار میباشد در آن به کار نرفته باشد. ما نیز از این قاعده مستثنی نخواهیم بود و در نهایت همه مداراتی که پیادهسازی میکنیم از نوع ترتیبی، و البته ترتیبی سنکرون خواهند بود. اما برای اینکه از اول شروع این مجموعه قرار بر این بود که از سطح مبتدی و از پایه مطالب بیان گردد، و تا حد امکان تمامی سرفصلها آموزش داده شوند، ابتدا با مدارهای ترکیبی و نحوه پیادهسازی آنها آشنا خواهیم شد ولی در نهایت ما تقریبا در هیچ یک از پیادهسازیها یک مدار مطلقا ترکیبی نخواهیم داشت. همانطور که در بالا اشاره شد مدارهای نهایی ما از نوع ترتیبی سنکرون هستند. ترتیبی سنکرون چیست؟

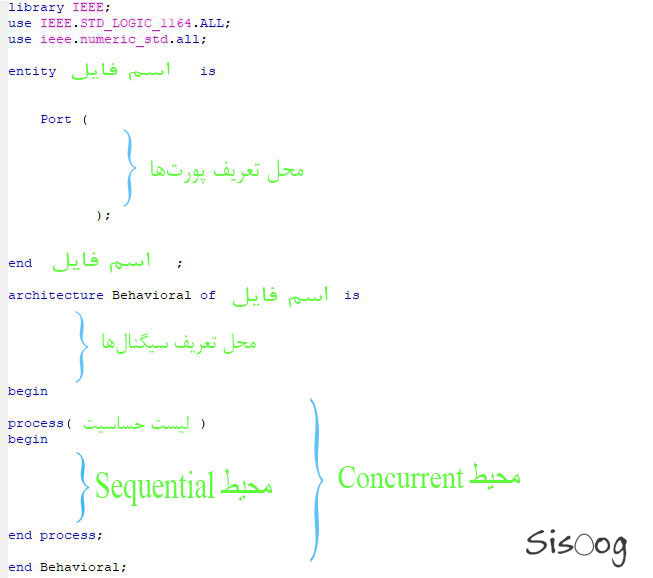

الگو و ساختار کد در زبان VHDL

الگوی کلی یک کد به صورت مختصر در بالا نمایش داده شده است. تصویر بالا به خوبی محیطهای مختلف و کاربرد آنها را نشان میدهد، اما به صورت کاملتر و دقیقتر در زیر به توضیح هر کدام خواهیم پرداخت:

اسم فایل: محلی که ما باید یک اسم دلخواه برای فایل VHDL (نه اسم پروژه) تعریف کنیم و دقیقا همان نام را در دو مکان دیگر، که در تصویر مشخص کردیم دوباره بنویسیم. البته اگر از Wizard استفاده کرده باشیم این کار به صورت خودکار انجام خواهد گرفت.

محل تعریف پورتها: در این محل ما باید ورودی-خروجیهایی را که در نهایت قرار است به پین های FPGA متصل شوند تعریف میکنیم.

محل تعریف سیگنالها: در این محل ما باید عواملی را تعریف کنیم که قرار است بعدا تبدیل به سیم یا رجیستر (حافظه) شوند. به محل تعریف سیگنالها دقت کنید، محل تعریف دقیقا قبل از begin مربوط به architecture میباشد.

حال اینکه سیگنالها چه موقع تبدیل به سیم و چه موقع تبدیل به رجیستر میشوند را طلبکار ما باشید تا بهش برسیم.

توجه کنید که برخلاف پورتها، سیگنالها عوامل داخلی هستند و قرار نیست که در نهایت مشخصا خودشان پورت ورودی-خروجی باشند. ولی میتوانند به پورتها ارجاع داده شوند که اتفاقا ما در ادامه همین کار را خواهیم کرد.

لیست حساسیت: عواملی هستند که با تغییر آنها process فعال خواهد شد، در واقع میتوان گفت بدون تغییر روی لیست حساسیت، process عملا هیچ کاری انجام نمیدهد.

محیط Concurrent: محلی که ما برای توصیف مدار ترکیبی از آن استفاده میکنیم. کدهایی که ما در این محل مینویسیم در نهایت تبدیل به یک سختافزار ترکیبی خواهند شد. دقت کنید که محیط Concurrent دقیقا بعد از begin مربوط به architecture میباشد.

محیط Sequential: محلی که ما برای توصیف مدار ترتیبی از آن استفاده میکنیم. این محیط نیز دقیقا بعد از begin مربوط به process میباشد. فرض کنید در لیست حساسیت، ما فقط کلاک را قرار دادیم و با تغییر کلاک، process فعال میشود و یک سری اعمال منطقی صورت میپذیرد، اگر کمی با مدار منطقی آشنا باشید میدانید که همین موضوع توصیف یک مدار ترتیبی خواهد بود.

برای آشنا شدن بیشتر با محیط ترکیبی به کد زیر توجه کنید:

|

1 2 3 |

A <= B AND C; D <= C; |

قبل از هر چیزی توجه کنید که ما با استفاده از “=>” سمت راست را به سمت چپ ارجاع میدهیم.

اولویت

اگر مطالب قبلی را به خوبی دنبال کرده باشید، حتما این نکته را میدانید که هیچگونه اولویتی وجود ندارد و این دو خط کد اولویت یکسانی دارند و ارجاع تنها با تغییر مقادیر سمت راستی صورت میپذیرد. یعنی اگر مقدار C تغییر کند خط اول و دوم ارجاعاتشان همزمان خواهد بود.

پس طبق تعریفهای بالا میتوان گفت که کد زیر دقیقا معادل با کد بالا خواهد بود:

|

1 2 3 |

D <= C; A <= B AND C; |

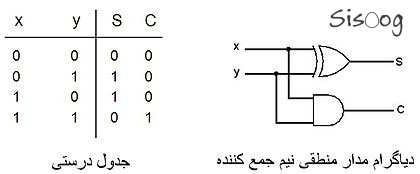

Half Adder (نیم جمع کننده)

قصد داریم مدار ساده نیم جمع کننده را در FPGA پیادهسازی کنیم، اما قبل از آن با خود مدار و منطق مدار آشنا خواهیم شد که بعد بتوانیم همین منطق را پیادهسازی کنیم.

تصویر بالا به خوبی مدار نیم جمع کننده را توصیف میکند، ما فقط با توجه به جدول درستی مقادیر توابع خروجی را استخراج میکنیم، که به صورت زیر خواهند بود:

S = x ⊕ y

C = x . y

الان فقط کافیست همین دو خط بالا را به زبان VHDL، در محیط Concurrent بنویسیم، کل کد ما به صورت زیر خواهد بود:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 |

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity Example2 is Port ( x : in STD_LOGIC; y : in STD_LOGIC; S : out STD_LOGIC; C : out STD_LOGIC ); end Example2; architecture Behavioral of Example2 is begin S <= x xor y; C <= x and y; end Behavioral; |

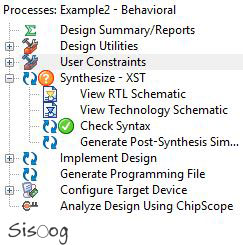

پس از اینکه کد را نوشتیم، میتوانیم کد را از لحاظ صحت Syntax بررسی کنیم. برای این کار باید مانند تصویر زیر روی گزینه Check Syntax دابل کلیک کنیم، اگر کنار این گزینه مانند تصویر زیر سبز رنگ شد کد ما از لحاظ Syntax هیچگونه مشکلی ندارد.

در پایان اضافه کنم که شاید بعضی از دوستانی که قبلا یک آشنایی اولیه با این FPGA داشتند، منتظر هستند که هرچه سریعتر از مطالب ابتدایی گذر کنیم، ولی در نظر بگیرید که در میان خوانندگان این مجموعهی آموزشی، افرادی هستند که شاید اولین بار باشد که اسم FPGA به گوششان میخورد، پس کمی صبور باشید، به وقتش مطالبی را بیان خواهیم کرد که برای شما نیز تازگی خواهند داشت. و دوستان مبتدی نیز در روند آموزش سعی کنند به مطالب جزئی مانند کلمات کلیدی، Syntax و دیگر نکات زبان VHDL که شاید بعضا توضیح داده نشوند توجه خاص کنند.

در قسمت پنجم در مورد پورتها، سیگنالها و اینکه چگونه یک ماژول را به ماژول دیگر اضافه کنیم، صحبت خواهیم کرد، پس با سیسوگ همراه باشید.

سیسوگ با افتخار فضایی برای اشتراک گذاری دانش شماست. برای ما مقاله بنویسید.