معماری پردازندههایRISC_V را بهتر بشناسیم

قسمت 1از زمان بهوجودآمدن کامپیوترها هر روزه تلاش شده تا کامپیوترهای بهتری بسازند که مشکلات قبل رو نداشته باشد، اگر به تاریخ کامپیوترها نگاهی بیندازید متوجه خواهید شد که هیچوقت توسعهدادن کامپیوتر متوقف نشده و همیشه سعی بر بهتر کردن کامپیوترها کردن، این تلاشها برای بهتر کردن کامپیوترها همیشه فقط در بعد سایز ترانسیستور یا جریان مصرفی و یا هزاران مؤلفه دیگر نبودند، گاهی تلاشها برای بهتر کردن ساختار داخلی پردازنده بوده است اگر یک سرچ ساده در اینترنت بکنید لیست کاملی از همه معماریهایی که تا به امروز ساخته شدن رو میبینید.

از بین همه این معماریها موضوع این سری آموزشها و مقالهها با RISC_V هست، این معماری تقریباً معماری جدیدی است و دوستان در سیسوگ قبلاً در مورد آن صحبت کردهاند، ما هم کمی در اول راه مقاله به آن میپردازیم.

پردازندههای RISC سبکی از معماری پردازندهها هستند که از مجموعهای محدود و ساده از دستورالعملها استفاده میکنند. در این معماری، تمرکز بر روی سرعت اجرای دستورات و بهرهوری بالاست. برخلاف معماری CISC (Complex Instruction Set Computer) که دستورات پیچیده و گستردهتری دارد،RISC بهجای آن از دستورات سادهتر و معماری سادهتر استفاده میکند.

ویژگی های معماری RISC

بعضی از ویژگیهای معماری RISC شامل موارد زیر است:

- استفاده از دستورات ساده و معمولاً یکانی: دستورات در RISC معمولاً سادهتر و کوتاهتر هستند و بهصورت یکانی (بدون ترکیب دستورات) عمل میکنند.

- تعداد محدودی دستورات: معماری RISC با مجموعهای محدود از دستورات عمل میکند که به افزایش سرعت و کاهش پیچیدگی معماری کمک میکند.

- اجرای سریع دستورات: با استفاده از دستورات ساده، اجرای دستورات در پردازندههای RISC به طور معمول سریعتر از CISC است.

- باریکه ساختاری: معماری RISC معمولاً دارای ساختارهای سادهتر و باریکهتری است که به بهرهوری و کارایی بالاتر کمک میکند.

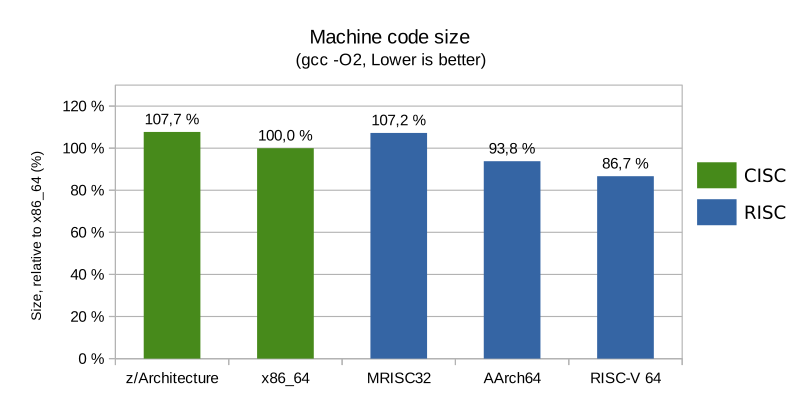

اندازه کد معماری های مختلف برنامه نویسی

تفاوت RISC و RISC_V

(Reduced Instruction Set Computer) RISC

RISC یک رویکرد در طراحی معماری پردازنده است که بر این اصل استوار است که با استفاده از مجموعهای کوچک و ساده از دستورات، عملکرد پردازندهها را بهبود بخشیده و پیچیدگی آنها را کاهش دهد.

مثالهای از معماریهای RISC شامل MIPS،ARM و SPARC هستند.

RISC-V

RISC-V نیز یک نوع از معماری RISC است، اما بهعنوان یک استاندارد آزاد و متنباز برای معماری پردازندهها مطرح است. بهعبارتدیگر، RISC-V یک مجموعه از دستورات و رابطهای برنامهنویسی است که توسط پردازندهها باید پشتیبانی شود.

RISC-V متنباز بوده و اجازه میدهد که آن را باتوجهبه نیازهای خود توسعه دهند و تصحیحات لازم را اعمال کند.

این استاندارد ابزار قدرتمندی برای توسعهدهندگان است و بهویژه برای افراد و شرکتهایی که میخواهند پردازندههای خود را طراحی کنند. ازاینرو، اصطلاح RISC به معماری کلی اشاره دارد، درحالیکه RISC-V یک استاندارد خاص در این معماری است که باز و آزاد است.

مقایسه RISC_V با ARM محبوب ما

مقایسه RISC_V با ARM

همانطور که بالاتر نیز اشاره شد ARM هم از معماری RISC استفاده میکند، اما اپنسورس نیست و به مالکیت شرکت ARM هست که این خود باعث میشوند که شخصیسازی کمتری بتوان روی آن انجام داد، اما خب این مباحث زیاد به ما طراحان مربوط نیست، ما که نمیخوابم یک پردازنده بسازیم یا شخصیسازی کنیم، چیزی که برای ما مهمه طریقه برنامهنویسی، قیمت و سرعت آن است، در میان دو پردازنده ARM و RISC_V نمیشود آنچنان تفاوت سرعت پردازشی رو دید و بیشتر به پارامترهایی مثل فرکانس پردازنده، بهینگی معماری، اندازه کشهای حافظه، و پیادهسازی فیزیکی بستگی دارد.

تاریخچه پردازندههای RISC_V چرا بهش میگیم معماری جوان؟

ایده و منشأ معماری RISC-V در دانشگاه کالیفرنیای برکلی (UC Berkeley) در دهه 2000 مطرح شد و این پروژه به عنوان بخشی از طرح “بهبود معماریهای پردازنده” آغاز شد.

نیازی که به یک معماری آزاد حس میشد چرخهای توسعه این معماری با سرعت هرچهتمامتر هل داد و باعث شد که اولین نسخه عمومی این تراشه در سال 2010 به عنوان RISC_V (Public Release 1.0) به همراه مجموعهای از دستورالعملها، رابطهای برنامهنویسی، و ساختارهای پایه برای پردازنده.

این معماری آزاد بهسرعت جای پای خودش رو در مراکز تحقیقات یارانهای باز کرد و طولی نکشید که استفاده از این معماری بین مهندسان و طراحان افزایش یافت.

ولی خب همانطور که بالاتر مطرح شد، هیچ ویژگی چشمگیری که باعث شود معماری RISC_V را بهتر از بقیه بدانیم ندارد. اما به علت آزاد بودن آن شرکتهای سازنده چیپ، میتوانند چیپهای ارزانتری با ویژگیهای بسیار خوب روانه بازار کنند.

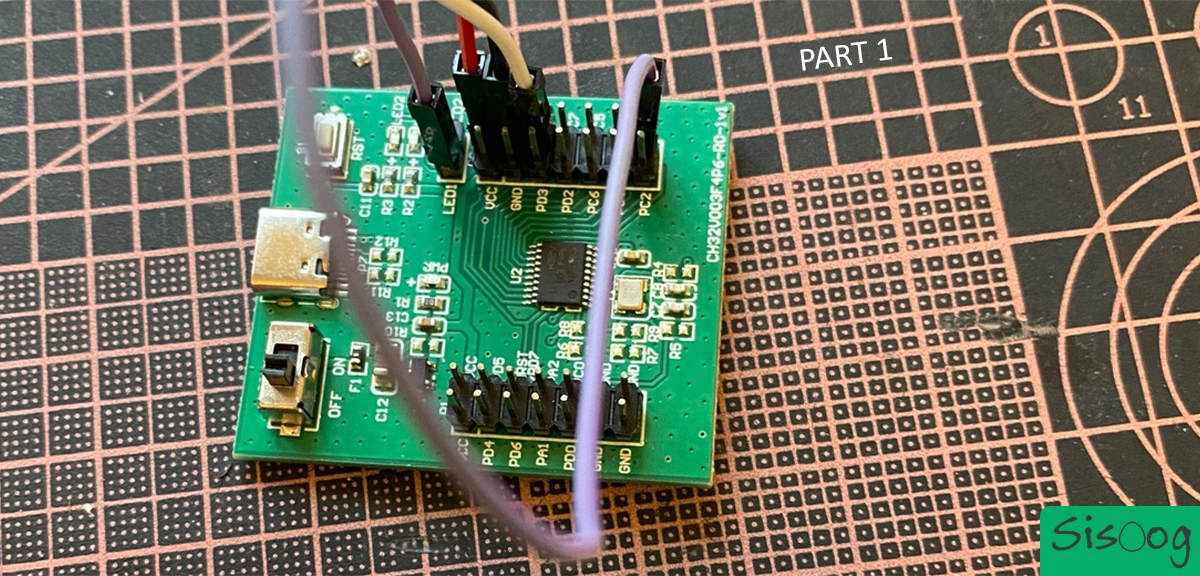

ساختار داخلی یک میکروکنترلر بر اساس پردازندهای با معماری RISC_V

در عکس زیر دیاگرام داخلی یک میکرو رو میبینید که از شرکت WCH هست و میخواهیم در این آموزشها با آنها کار کنیم

در پس از بررسی دیاگرام متوجه خواهیم شد که بسیار شبیه به میکروکنترلرهایی بر اساس هستههای ARM هستند، این دیاگرام داخلی میکرو کنترلی هست که میخواهیم در آینده با آن کار کنیم. برخی از قابلیتهای آن نیز در زیر آمده است که خدایی کم نذاشتن:

| ویژگی (Feature) | جزئیات (Details) |

|---|---|

| پردازنده (CPU) | Qingke V4F – فرکانس تا ۱۴۴MHz (up to 144MHz system clock) |

| واحد محاسباتی (Math Unit) | ضرب تکسیکلی، تقسیم سختافزاری، FPU (Single-cycle MUL, HW DIV, Float Point Unit) |

| حافظه (Memory) | ۶۴KB SRAM، ۲۵۶KB Flash |

| ولتاژ تغذیه (Power Supply) | ۲.۵V / ۳.۳V – GPIO با تغذیه مستقل (independent supply) |

| حالتهای کممصرف (Low Power Modes) | Sleep / Stop / Standby |

| ریست و نظارت تغذیه (Reset & Voltage Monitor) | POR/PDR، PVD قابل برنامهریزی |

| DMA | ۲ کنترلر، مجموعاً ۱۸ کانال (2 controllers, 18 total channels) |

| تقویتکنندهها (Amplifiers) | ۴ عدد |

| مولد تصادفی (TRNG) | یک عدد (True Random Number Generator) |

| مبدل دیجیتال به آنالوگ (DAC) | ۲ کانال ۱۲ بیتی (2 × 12-bit DACs) |

| مبدل آنالوگ به دیجیتال (ADC) | ۲ × ۱۶ کاناله ۱۲ بیتی + ۱۶ کانال TouchKey |

| تایمرها (Timers) | ۱۰ عدد |

| رابط USB | USB 2.0 OTG (Full-speed)، Host/Device (High-speed, 480Mbps with PHY) |

| رابطهای سریال (Serial Interfaces) | ۳ × USART، ۵ × UART |

| رابط CAN | ۲ عدد، نسخه 2.0B فعال |

| رابطهای جانبی دیگر (Other Interfaces) | SDIO، FSMC، DVP |

| I²C / SPI / IIS | ۲ × IIC، ۳ × SPI، ۲ × IIS |

| اترنت (Ethernet) | Gigabit Ethernet + PHY داخلی ۱۰M |

| ورودی/خروجیها (I/O Ports) | ۸۰ پورت – قابل نگاشت به ۱۶ وقفه خارجی |

| CRC | واحد محاسبه CRC (CRC Calculation Unit) |

| شناسه یکتا (Unique ID) | ۹۶ بیت (96-bit) |

| دیباگ (Debug) | رابط سریال ۲ سیمه (2-wire Serial Debug Interface) |

| بستهبندی (Package) | LQFP64M، LQFP100 |

معرفی و آموزش کارکردن با پردازندههایی بر اساس این معماری از شرکت WCH

به هر حال، مقالات مشابهی در سیسوگ موجود است و این مباحث مقدمهای برای مسیر پیش روی ماست؛ میتوان این جلسه را “پیشگفتار” نامید.

شرکتهای بزرگ و کوچک متعددی وجود دارند که پردازندههایی بر اساس معماری RISC-V تولید و عرضه کردهاند، و با یک جستجوی ساده میتوانید فهرست آنها را بیابید. در این سری آموزشها، ما با شرکت WCH کار خواهیم کرد، شرکتی که شاید برایتان چندان ناآشنا نباشد، به ویژه با محصولاتی مانند سری CH32V.

ما در ادامه آموزشها، روش کار و برنامهنویسی میکروکنترلرهای شرکت WCH را که بر پایه معماری RISC-V هستند، آغاز میکنیم. برای نمونه، تمرکز اصلی بر مدلهایی مانند CH32V003 و به طور خاص CH32V003F4P6 خواهد بود، که از سری CH32V هستند و ویژگیهای خوبی را ارائه میدهند. این مدلها، مانند CH32V003F4P6، با قیمت مناسب و قابلیتهای بالا، گزینهای ایدئال برای توسعهدهندگان هستند و ما چندین بار در آموزشها از CH32V، CH32V003 و CH32V003F4P6 برای مثالهای عملی استفاده خواهیم کرد تا درک عمیقتری از برنامهنویسی و پیادهسازی فراهم شود.

در جلسه بعدی، با میکروکنترلرهای این شرکت، نرمافزارها و سختافزارهای مورد نیاز آشنا میشویم. این آموزشها به شما کمک میکند تا به طور حرفهای با سری CH32V، از جمله CH32V003 و CH32V003F4P6، کار کنید و پروژههای واقعی بسازید.

سیسوگ با افتخار فضایی برای اشتراک گذاری دانش شماست. برای ما مقاله بنویسید.